On-Chip Ultra-Fast Data Acquisition System for Optical Scanning Acoustic Microscopy Using  $0.35\mu m$  CMOS Technology

Peiliang Dong, MSc, BSc

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy September 2008

#### Abstract

Optical Scanning Acoustic Microscopy (OSAM) is a non-contacting method of investigating the properties and hidden faults of solid materials. This thesis presents an ultra-fast data acquisition system (DAQ) which samples and digitises the output signal of OSAM. The author's work includes the design of the clock source and the sampler, and integration of the whole system.

The clock source is a unique pulse generator based on a 2.624GHz PLL with a Quadrature VCO (QVCO), which is able to generate 4 clock signals in accurate quadrature phase difference. The pulse generator used the 4-phase clocks to provide control pulses to the sampler. The pulses were carefully aligned to the clock edges by digital logic, so that jitters were reduced as much as possible. The required short time delay for the sampler was also provided by the pulse generator, and this was implemented by a smartly-controlled switch box which re-shuffles the 4-phase clocks.

The presented sampler is a novel 10.496GSample/s Sub-Sampling Sample-and-Hold Amplifier (SHA). The SHA sampled the input, and transformed its spectrum down to a low-frequency range so that it can be digitised. Charge-domain sampling strategy and double differential switches were both developed in this circuit to significantly improve the sampling speed. The periodicity of the system input was exploited in repetitive sampling to reduce the noise.

These designed modules were integrated into a DAQ for a  $2 \times 8$  sensor array. A pseudo-parallel scanning strategy was presented to minimise the power consumption, and a current-based buffer was applied to deliver the control pulses into the array.

The DAQ was implemented on-chip in a low-cost  $0.35\mu m$  standard CMOS process. The measurement results showed that the DAQ successfully achieved a sampling rate more than 10GS/s, with a maximum output resolution of approximately 6 bits.

#### Acknowledgments

I'd like to thank my supervisors, Dr. Ian Harrison and Dr. Barrie Hayes-Gill, for their guidance and support during my PhD study. I am especially grateful to Ian, and feel lucky to have him as my supervisor, who not only taught me the essential skills of RF design and measurement, but also gave me valuable ideas whenever I had problems in my research. Without his inspiration and support, I could not make this achievement.

I'd also like to thank Roger, who provided technical support for the chip fabrication, Richard, who made the optical set-up for the chip measurement, and one of my best friends Proust (Mengxiong), who designed the front-end circuits. Thanks also go to my colleagues and friends in the School of EEE past and present, with whom I have been exchanging ideas and knowledge, and having happy times as well. These include Proust, Vinoth, Fen, Li, Sue, Shah, Qidong, Fred, David, Sheng, Wilson, Irene, Maggie, Yueran, etc.

I'd like to express my gratitude to the Si Yuan Foundation for funding my PhD study, and EPSRC for funding this work (Grant No. EP/CS12758/1).

Lastly, I would express my greatest thanks to my wife, Bei, who constantly supports me on everything, and also my parents, my sister, and my parents-in-law for their support. Finally, best wishes to my daughter Catherine, who is just 6 months older than this thesis, and has totally no idea of what is going on here.

### **Abbreviation List**

ADC Analog-to-Digital Converter

$\mathbf{CML}$  Current-Mode Logic

CMOS Complementary Metal Oxide Semiconductor

CW Laser Continuous-Wave Laser

**DAQ** Data AcQuisition

$\mathbf{DC\text{-}Op}\ \mathrm{DC}$  Operating Point

**DDS** Double Differential Switch

$\mathbf{DDU}$  Digital Delay Unit

$\mathbf{DFT}$  Digital Fourier Transform

**DLL** Delay-Locked Loop

$\mathbf{DSP}\ \operatorname{Digital\ Signal\ Processor}$

ECL Emitter-Coupled Logic

${\bf FD}\;$  Frequency Divider

$\mathbf{FFT}$  Fast Fourier Transform

IDFT Inverse Digital Fourier Transform

IFFT Inverse Fast Fourier Transform

**LFA** Linearising Feedback Amplifier

OSAM Optical Scanning Acoustic Microscopy

**OpAmp** Operational Amplifier

${f PD}$  Phase Detector

**PFD** Phase/Frequency Detector

**PLL** Phase-Locked Loop

${\bf QVCO}$ Quadrature Voltage-Controlled Oscillator

$\mathbf{RGC}$  ReGulated Cascode

${f RMS}$  Root Mean Square

**SAW** Surface Acoustic Wave

$\mathbf{SCL}$  Source-Coupled Logic

SHA Sample-and-Hold Amplifier

$\mathbf{TCA}$  Trans-Conductance Amplifier

${\bf TIA}\;$  Trans-Impedance Amplifier

${\bf VCO} \ \ {\bf Voltage\text{-}Controlled} \ \ {\bf Oscillator}$

# **Brief Contents**

| Tables of ContentsVI                       |

|--------------------------------------------|

| I Introduction to O-SAM and its DAQ system |

| II Clock Source and Pulse Generator10      |

| III Sub-Sampling SHA84                     |

| IV On-Chip Data Acquisition System         |

| V Implementation, Measurement, and Summary |

| VI Appendix                                |

| Bibliography and Index                     |

# Contents

| $\mathbf{Abs}$ | tra  | ct                                                            | Ι   |

|----------------|------|---------------------------------------------------------------|-----|

| Ack            | no   | m wledgements                                                 | II  |

| Abł            | ore  | viation List                                                  | III |

| Brie           | ef C | ${f Contents}$                                                | V   |

| Tab            | le ( | of Contents                                                   | ΧI  |

| ${f List}$     | of   | Figures XV                                                    | III |

| ${f List}$     | of   | Tables X                                                      | IX  |

| I              | Int  | croduction to O-SAM and its DAQ system                        | 1   |

| 1 (            | Opt  | ical Scanning Acoustic Microscopy                             | 2   |

| 1              | .1   | Optical Scanning Acoustic Microscopy (the optical part)       | 2   |

| 1              | 2    | Data Acquisition (DAQ) system for O-SAM (the electronic part) | 4   |

| 1              | .3   | Thesis organization                                           | 6   |

| CC | CONTENTS                    |                                                  |    |  |

|----|-----------------------------|--------------------------------------------------|----|--|

| 2  | System Architecture         |                                                  |    |  |

|    | 2.1                         | Structure and function description               | 7  |  |

|    | 2.2                         | Thesis objectives                                | 8  |  |

| II | $\mathbf{C}$                | lock Source and Pulse Generator                  | 10 |  |

| 3  | Intr                        | oduction to Clock Synthesiser                    | 12 |  |

|    | 3.1                         | Phase-Locked Loop (PLL)                          | 12 |  |

|    | 3.2                         | Delay-Locked Loop (DLL)                          | 22 |  |

|    | 3.3                         | Generation of quadrature signals                 | 23 |  |

|    | 3.4                         | Summary                                          | 26 |  |

| 4  | Design of Clock Synthesiser |                                                  |    |  |

|    | 4.1                         | Solutions to the clock source in the DAQ $\dots$ | 27 |  |

|    | 4.2                         | Phase/Frequency Detector and charge pump         | 33 |  |

|    | 4.3                         | Frequency divider (FD)                           | 35 |  |

|    | 4.4                         | VCO                                              | 49 |  |

|    | 4.5                         | Loop filter                                      | 57 |  |

|    | 4.6                         | Simulation of clock synthesiser                  | 59 |  |

|    | 4.7                         | Summary                                          | 61 |  |

| C  | CONTENTS VIII           |                                                        |    |

|----|-------------------------|--------------------------------------------------------|----|

| 5  | Pul                     | se Generator                                           | 63 |

|    | 5.1                     | System requirement of the pulse generator              | 63 |

|    | 5.2                     | Architecture and mechanism of the pulse generator      | 65 |

|    | 5.3                     | Switch box                                             | 70 |

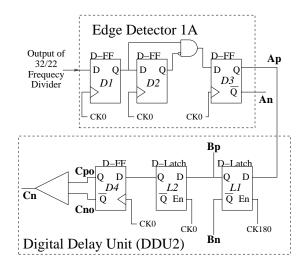

|    | 5.4                     | Digital Delay Unit and Edge Detector 1                 | 72 |

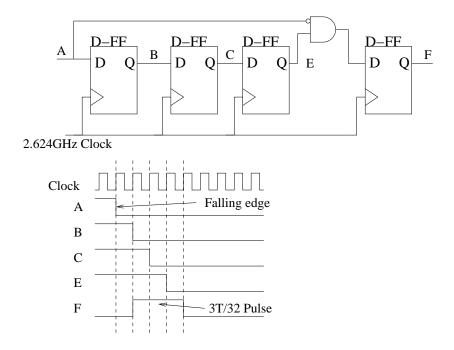

|    | 5.5                     | 32/33 Frequency divider (32/33 FD) and Edge Detector 2 | 75 |

|    | 5.6                     | Low-frequency dividers                                 | 77 |

|    | 5.7                     | Layout and simulation                                  | 79 |

|    | 5.8                     | Design of Pulse Generator for $2.6GS/s$ DAQ            | 79 |

|    | 5.9                     | Summary                                                | 82 |

|    |                         |                                                        |    |

| II | III Sub-sampling SHA 84 |                                                        |    |

| 6  | Intr                    | roduction to SHA                                       | 86 |

|    | 6.1                     | Sample-and-Hold Amplifier (SHA)                        | 86 |

|    | 6.2                     | Sub-sampling                                           | 88 |

|    | 6.3                     | Switched-capacitor filter                              | 89 |

|    | 6.4                     | Summary                                                | 92 |

| 7  | Des                     | ign of Sub-sampling SHA                                | 93 |

|    | 7.1                     | System requirement of the SHA                          | 93 |

|    | 7.2                     | Sub-sampling for periodical signal                     | 94 |

| C | CONTENTS |                                                         |     |  |  |

|---|----------|---------------------------------------------------------|-----|--|--|

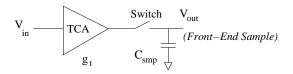

|   | 7.3      | Charge-domain sampling                                  | 96  |  |  |

|   | 7.4      | Double Differential Switch (DDS)                        | 98  |  |  |

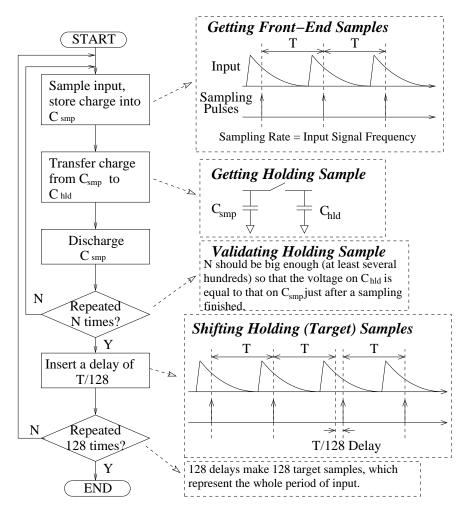

|   | 7.5      | Repetitive sampling                                     | 99  |  |  |

|   | 7.6      | Terminologies                                           | 101 |  |  |

|   | 7.7      | Implementation of Sub-Sampling SHA                      | 102 |  |  |

|   | 7.8      | Summary                                                 | 105 |  |  |

| 8 | Err      | ors and Correcting Circuits                             | 106 |  |  |

|   | 8.1      | Non-linearity output and Linearising Feedback Amplifier | 106 |  |  |

|   | 8.2      | Frequency Response and Compensating Filter              | 115 |  |  |

|   | 8.3      | System errors due to 4-phase clock source               | 120 |  |  |

|   | 8.4      | Architecture of Digital Filter                          | 133 |  |  |

|   | 8.5      | Summary                                                 | 138 |  |  |

| 9 | Noi      | se Analysis                                             | 139 |  |  |

|   | 9.1      | Noise folding and filtering in Sub-sampling SHA         | 139 |  |  |

|   | 9.2      | Filters in Sub-Sampling SHA                             | 140 |  |  |

|   | 9.3      | Consideration of flicker noise                          | 142 |  |  |

|   | 9.4      | Summary                                                 | 146 |  |  |

| CONTENTS | X |

|----------|---|

|          |   |

| IV           | On-Chip Data Acquisition System                | 148 |  |

|--------------|------------------------------------------------|-----|--|

| 10           | Front-End Circuits                             | 150 |  |

|              | 10.1 Photo-Diode                               | 150 |  |

|              | 10.2 TIA and LPF                               | 151 |  |

|              | 10.3 Summary                                   | 153 |  |

| 11           | DAQ for OSAM Sensor Array                      | 155 |  |

|              | 11.1 Power management                          | 155 |  |

|              | 11.2 SHA partition                             | 159 |  |

|              | 11.3 Interface to Pulse Generator              | 161 |  |

|              | 11.4 Array architecture                        | 163 |  |

|              | 11.5 Summary                                   | 166 |  |

| $\mathbf{V}$ | Implementation, Measurement, and Summary       | 167 |  |

| 12           | Implementation and measurement                 | 168 |  |

|              | 12.1 Specification of Chip RF2                 | 168 |  |

|              | 12.2 Measurement Results of <i>Prototype 1</i> | 172 |  |

|              | 12.3 Measurement Results of <i>Prototype 2</i> | 188 |  |

|              | 12.4 Summary                                   | 190 |  |

| 13           | Issues arising and further work                | 192 |  |

|              | 13.1 Current issues and possible solutions     | 192 |  |

|              | 13.2 Other possible improvements               | 196 |  |

| CONTENTS                               | XI  |

|----------------------------------------|-----|

| 14 Conclusions                         | 199 |

| VI Appendix                            | 204 |

| A Description of Chip RF1              | 205 |

| A.1 Review of the optimising theory    | 205 |

| A.2 Implementation                     | 207 |

| A.3 Simulation and measurement results | 207 |

| Bibliography and Index                 | 210 |

| Bibliography                           | 210 |

| Index                                  | 217 |

# List of Figures

| 1.1  | Optical set-up of OSAM                 |

|------|----------------------------------------|

| 2.1  | Architecture of DAQ system for OSAM    |

| 3.1  | Structure of Phase-Locked Loop         |

| 3.2  | Phase/Frequency Detector               |

| 3.3  | Charge Pump in PLL                     |

| 3.4  | Differential Negative-R VCO            |

| 3.5  | Spectrum of VCO output                 |

| 3.6  | Current Mode Logic                     |

| 3.7  | CML T-type Flip Flop                   |

| 3.8  | Delay-Locked Loop                      |

| 3.9  | RC-CR circuit                          |

| 3.10 | Structure of QVCO                      |

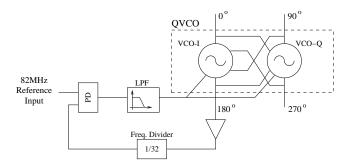

| 4.1  | Clock source solution 1: PLL with QVCO |

| Ι | LIST O | F FIGURES                                                                                        | XIII |

|---|--------|--------------------------------------------------------------------------------------------------|------|

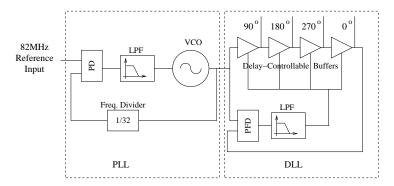

|   | 4.2    | Clock source solution 2: PLL followed by a DLL                                                   | 29   |

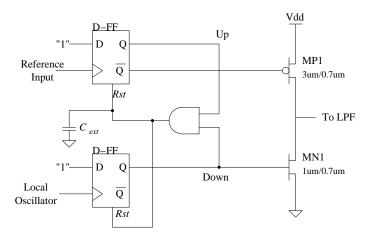

|   | 4.3    | Implementation of PFD and charge pump                                                            | 34   |

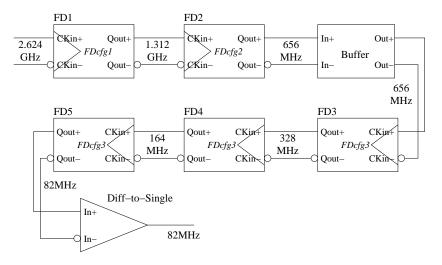

|   | 4.4    | CML frequency divider                                                                            | 35   |

|   | 4.5    | Divide-by-2 frequency divider                                                                    | 36   |

|   | 4.6    | Differential Buffer                                                                              | 36   |

|   | 4.7    | Differential to single-ended buffer                                                              | 37   |

|   | 4.8    | Comparison of the presented piecewise linear model and BSIM3 model                               | 38   |

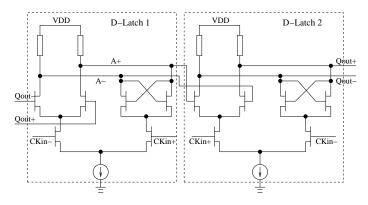

|   | 4.9    | SCL D-type latch                                                                                 | 39   |

|   | 4.10   | Modified D-latch circuits of the initial state of toggling                                       | 41   |

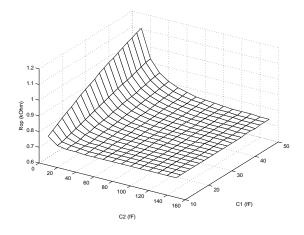

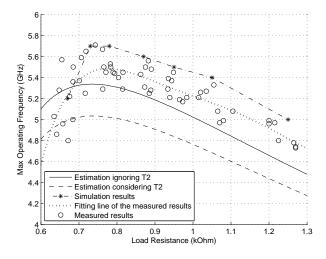

|   | 4.11   | Numerical solutions of optimum load resistance $R_{op}$                                          | 44   |

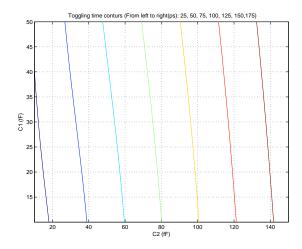

|   | 4.12   | Numerical solutions of toggling time $t_T$                                                       | 45   |

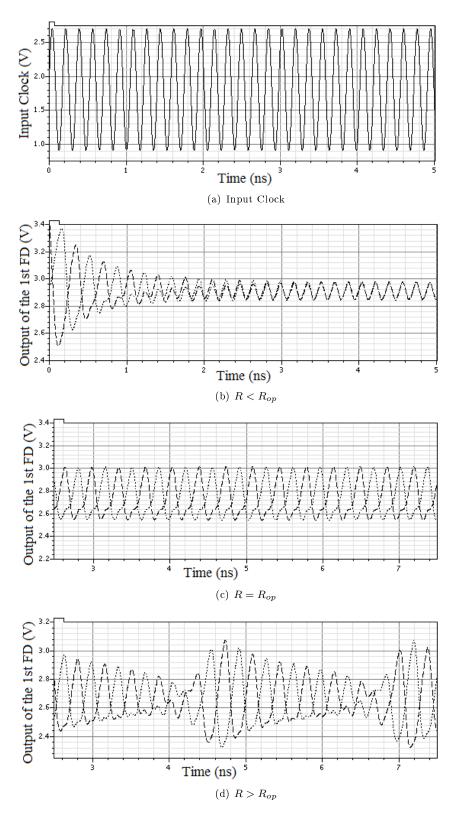

|   | 4.13   | Simulation results for different load resistor $R$                                               | 46   |

|   | 4.14   | Simulation and measurement results of maximum operating fre-                                     |      |

|   |        | quency                                                                                           | 47   |

|   | 4.15   | Quadrature Voltage-Controlled Oscillator                                                         | 50   |

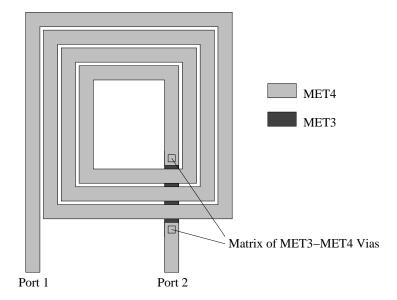

|   | 4.16   | Layout of of an on-chip inductor                                                                 | 52   |

|   | 4.17   | VCO for the $2.624GSample/s$ DAQ                                                                 | 56   |

|   | 4.18   | The 3rd-order loop filter in the presented PLL $\dots$                                           | 57   |

|   | 4.19   | System-level simulation of the PLL with QVCO                                                     | 59   |

|   | 4.20   | $V_{ctrl}({ m control} \ { m voltage} \ { m of \ the} \ { m QVCO})$ in post-layout simulation in |      |

|   |        | Cadence                                                                                          | 60   |

| LIST OF FIGURES | XIV |

|-----------------|-----|

|                 |     |

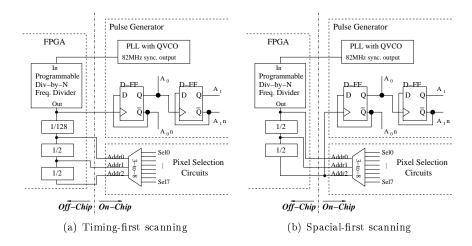

| 5.1  | Brief sampling procedure of the presented DAQ system $\dots$ | 64 |

|------|--------------------------------------------------------------|----|

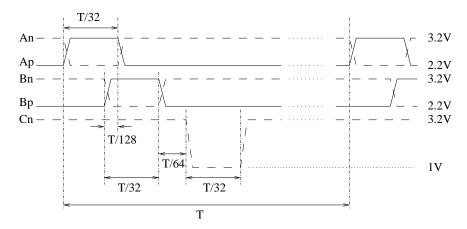

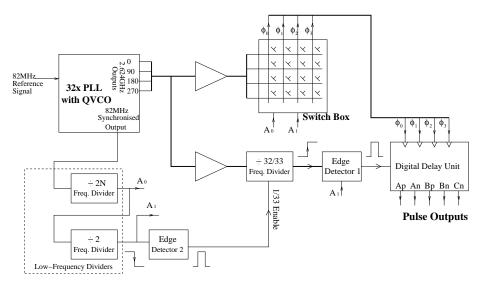

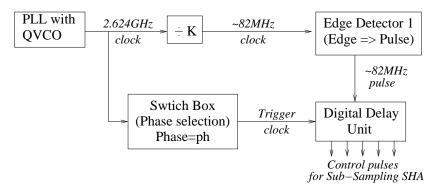

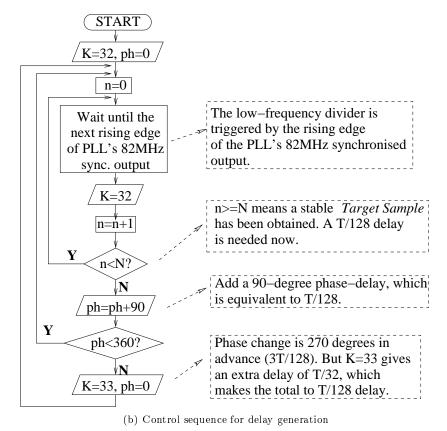

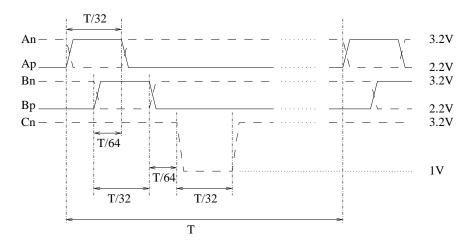

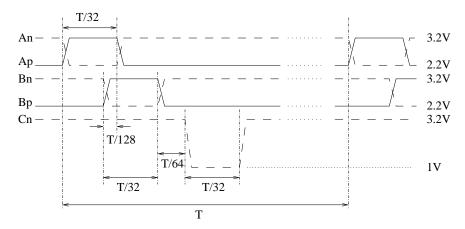

| 5.2  | Timing of control pulse signals for $10.5GS/s$ DAQ           | 65 |

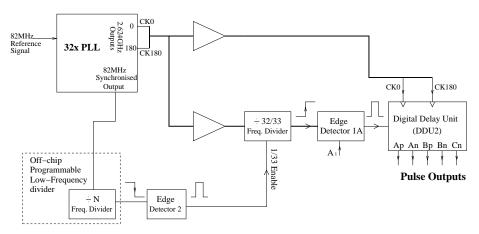

| 5.3  | Pulse Generator                                              | 66 |

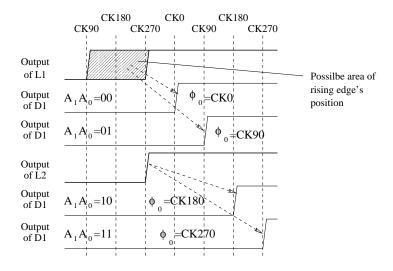

| 5.4  | Control mechanism of the presented pulse generator           | 68 |

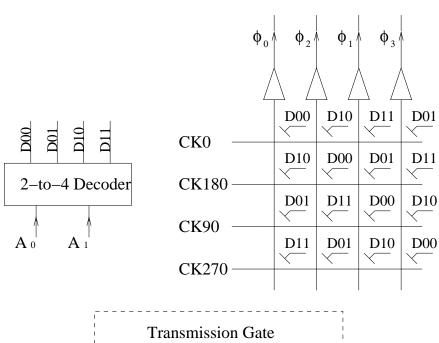

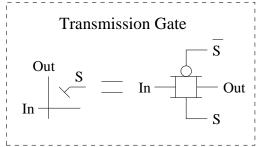

| 5.5  | Circuit diagram of Switch Box                                | 71 |

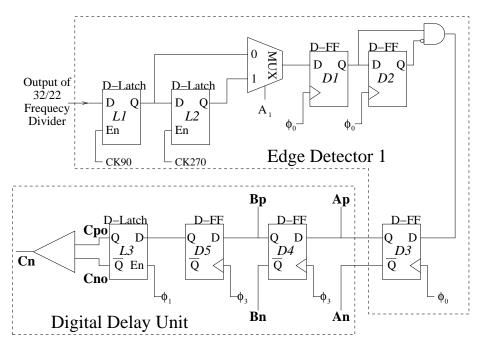

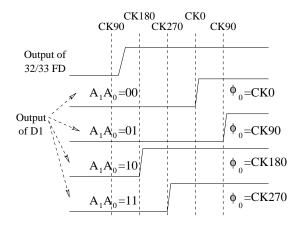

| 5.6  | Sketch of Edge Detector 1 and Digital Delay Unit             | 72 |

| 5.7  | Edge detection without synchronising                         | 73 |

| 5.8  | Edge detection with synchronising                            | 74 |

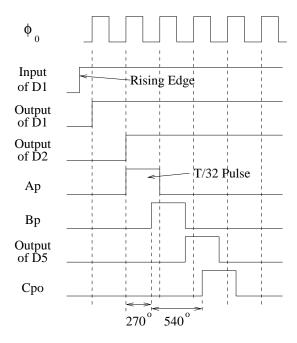

| 5.9  | Waveforms in Edge Detector 1 and Digital Delay Unit          | 75 |

| 5.10 | 32/33 Frequency Divider                                      | 75 |

| 5.11 | 2/3 Frequency Divider                                        | 76 |

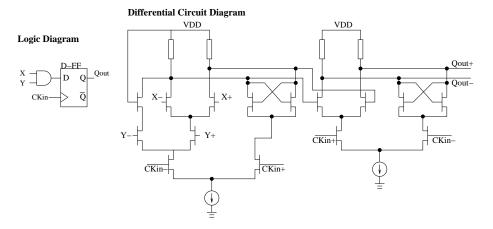

| 5.12 | Differential logic implementation of D-FF with AND gate      | 76 |

| 5.13 | Edge Detector 2                                              | 77 |

| 5.14 | Low frequency dividers                                       | 78 |

| 5.15 | Layout of Pulse Generator for $10.5GS/s$ DAQ                 | 78 |

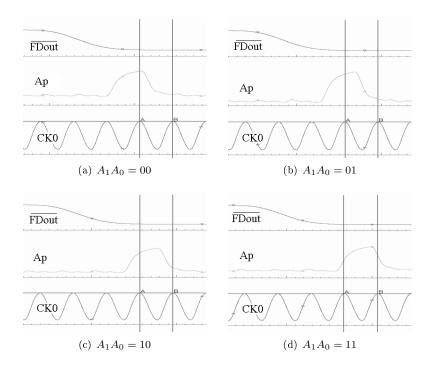

| 5.16 | Pulse Ap under different Switch Box configurations           | 80 |

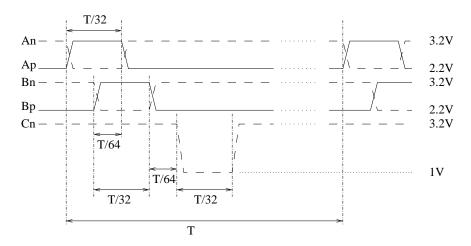

| 5.17 | Timing of control pulse signals for $2.6GS/s$ DAQ            | 80 |

| 5.18 | Pulse Generator for $2.6GS/s$ DAQ                            | 81 |

| 5.19 | Edge Detector 1 and Digital Delay Unit for $2.6GS/s$ DAQ     | 81 |

| 5.20 | Layout of Pulse Generator for $2.6GS/s$ DAQ                  | 82 |

| LIS | ST O | F FIGURES                                                       | XV  |

|-----|------|-----------------------------------------------------------------|-----|

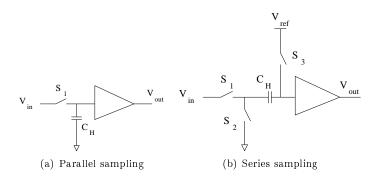

|     | 6.1  | Basic SHA techniques                                            | 87  |

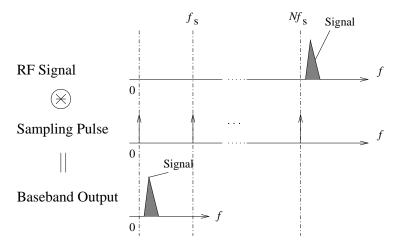

|     | 6.2  | Sub-sampling in frequency domain                                | 88  |

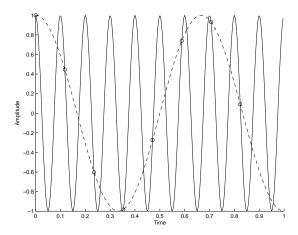

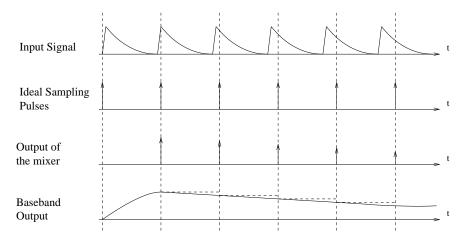

|     | 6.3  | Sub-sampling in time domain                                     | 89  |

|     | 6.4  | Noise folding in Sub-sampling Mixer                             | 90  |

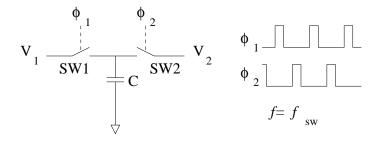

|     | 6.5  | Switched-capacitor as a resistor                                | 90  |

|     | 6.6  | 1st-order switched-capacitor low-pass filter                    | 91  |

|     | 7.1  | Architecture of DAQ system for OSAM                             | 94  |

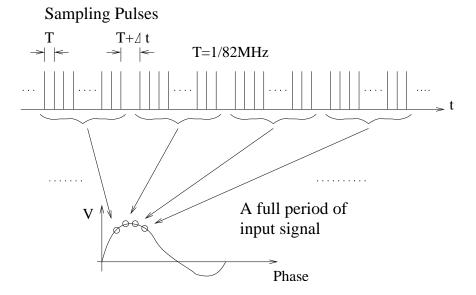

|     | 7.2  | Sub-sampling for periodical signal                              | 95  |

|     | 7.3  | Sub-sampling for periodical signal in time domain               | 96  |

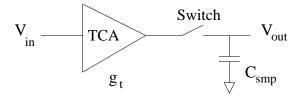

|     | 7.4  | Charge-domain sampling                                          | 97  |

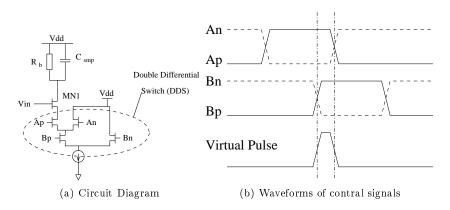

|     | 7.5  | SHA with Double Differential Switch                             | 98  |

|     | 7.6  | Repetitive sampling strategy                                    | 99  |

|     | 7.7  | Structure of proposed sub-sampling SHA                          | 100 |

|     | 7.8  | Operating procedure of the Sub-Sampling SHA                     | 101 |

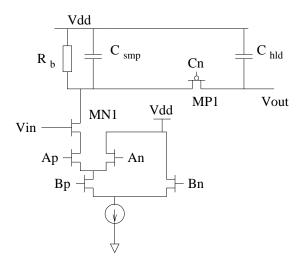

|     | 7.9  | Timing of switch control signals for $10.5GHz$ Sub-Sampling SHA | 103 |

|     | 7.10 | Timing of switch control signals for $2.6GHz$ Sub-Sampling SHA  | 104 |

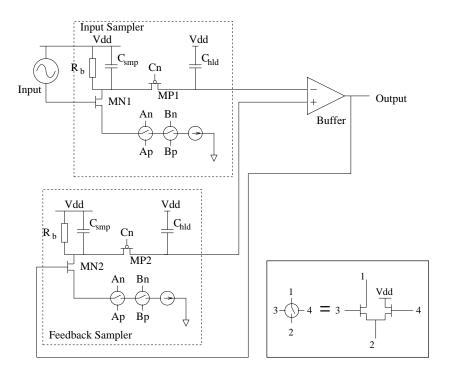

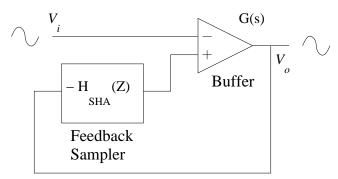

|     | 8.1  | Linearising Feedback Amplifier                                  | 108 |

|     | 8.2  | Feedback loop in LFA                                            | 109 |

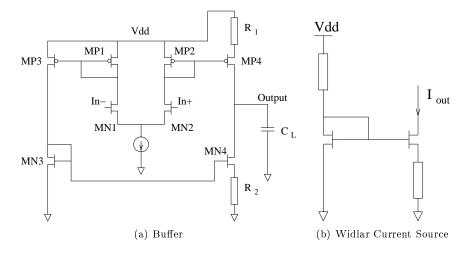

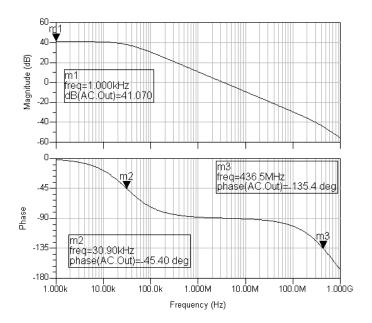

|     | 8.3  | High-Gain Low-Bandwidth Buffer                                  | 112 |

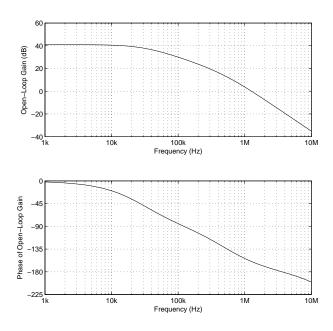

| 8.4  | AC simulation results of the present high-gain low-bandwidth Buffer        | 113 |

|------|----------------------------------------------------------------------------|-----|

| 8.5  | Bode Diagram of Equation (8.5)                                             | 114 |

| 8.6  | Idealised circuit for charge-domain sampling                               | 116 |

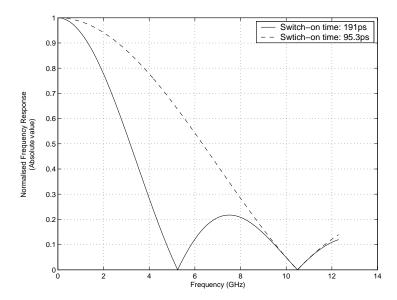

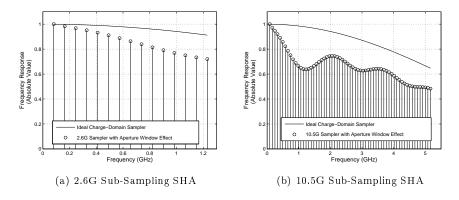

| 8.7  | Normalised frequency response of charge-domain sampling                    | 117 |

| 8.8  | Frequency response of proposed circuit in simulation                       | 119 |

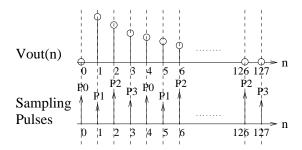

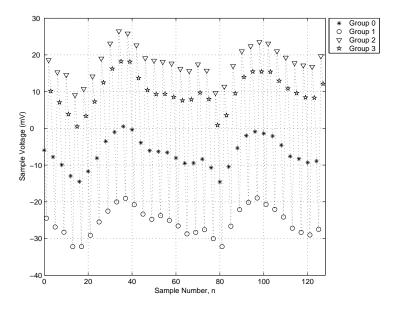

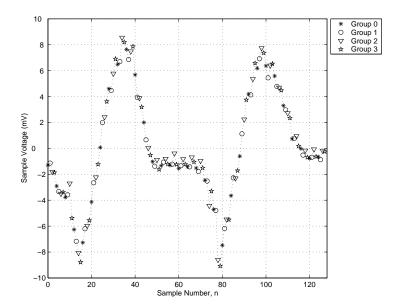

| 8.9  | 4 different $Virtual\ Pulses$ applied to $Target\ Samples\ V_{out}$        | 123 |

| 8.10 | Discretisation of Virtual Pulses                                           | 124 |

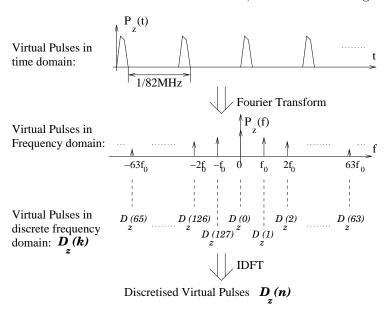

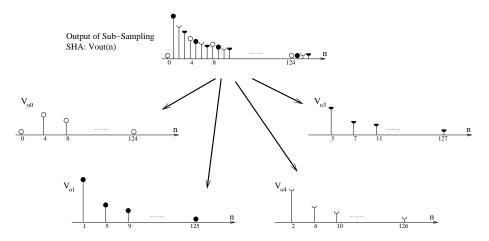

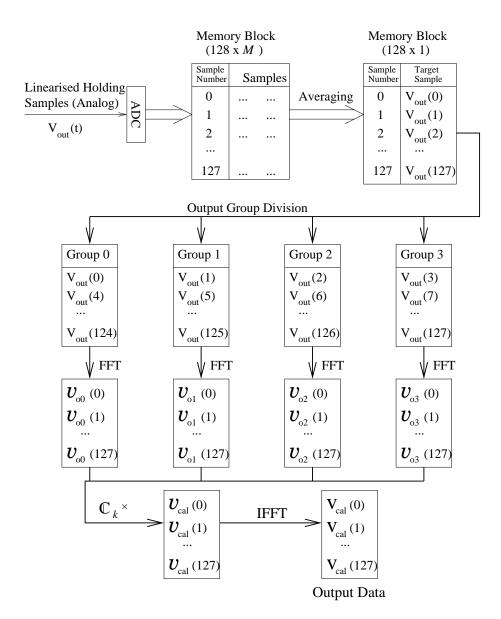

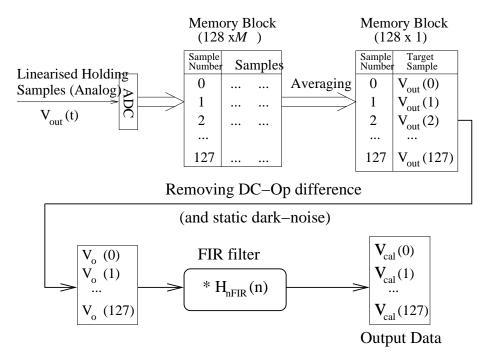

| 8.11 | Output Groups of SHA output                                                | 125 |

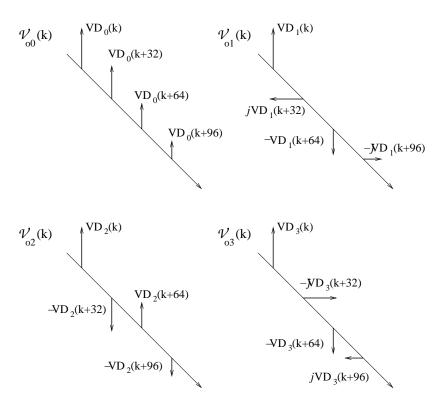

| 8.12 | Vectorial sum of $Output\ Groups$ in discrete frequency domain             | 127 |

| 8.13 | DC-Op difference among <i>Output Groups</i> when no calibration is applied | 132 |

| 8.14 | Output Groups removing DC-Op difference                                    |     |

| 8.15 | Digital Filter for the precise solution                                    | 134 |

| 8.16 | Digital Filter for the approximate solution                                | 136 |

| 9.1  | Noise filtering in Sub-Sampling SHA                                        | 140 |

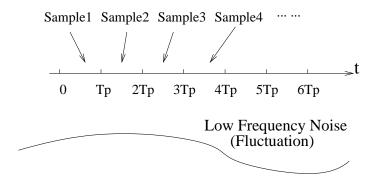

| 9.2  | Continuous sampling affected by low-frequency noise                        | 145 |

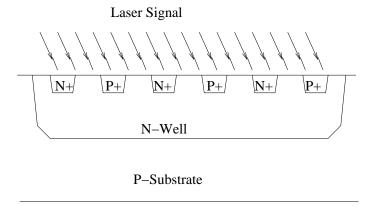

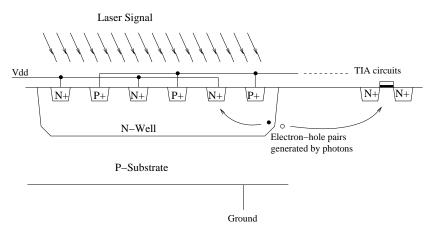

| 10.1 | Cross-section of the Photo-Diode implemented in AMS C35 $$                 | 151 |

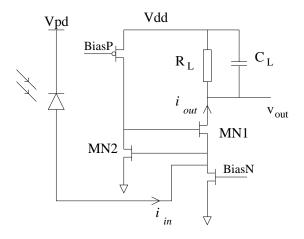

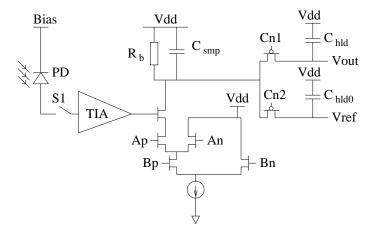

| 10.2 | Trans-Impedance Amplifier and Low-Pass Filter                              | 152 |

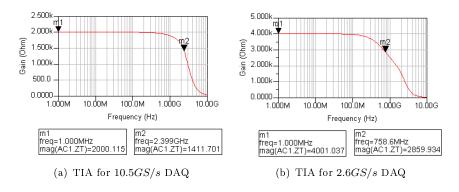

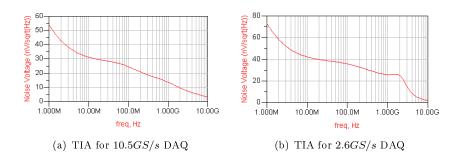

| 10.3 | Frequency response of TIA                                                  | 153 |

| 10.4 | Noise at the output of TIA                                                 | 153 |

| LIST OF FIGURES | XVII |

|-----------------|------|

| 11.1  | Implementation of pseudo-parallel array operating                           | 158 |

|-------|-----------------------------------------------------------------------------|-----|

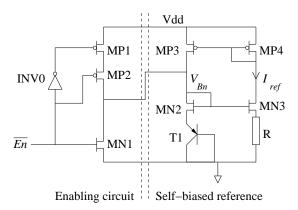

| 11.2  | Current source for TIA with enabling feature                                | 158 |

| 11.3  | Partition of Sub-Sampling SHA                                               | 160 |

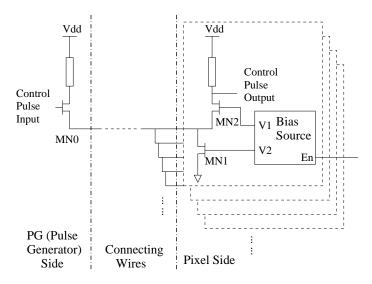

| 11.4  | Current-mode buffer for control pulses                                      | 162 |

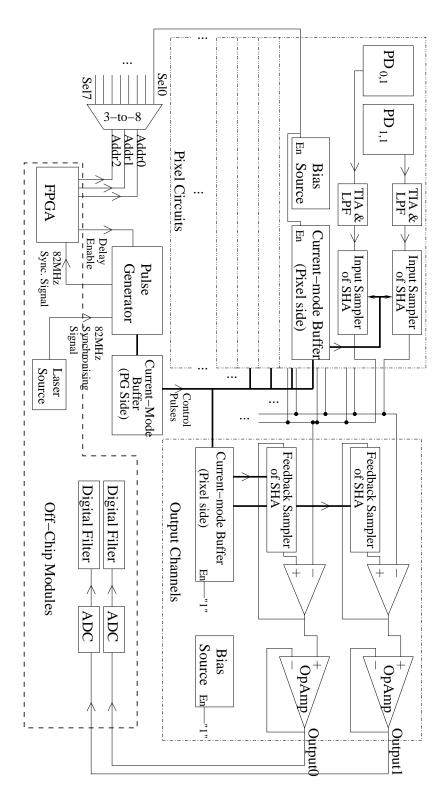

| 11.5  | DAQ system architecture for OSAM sensor array                               | 164 |

| 11.6  | Output channel for 1-D differential sensor array                            | 165 |

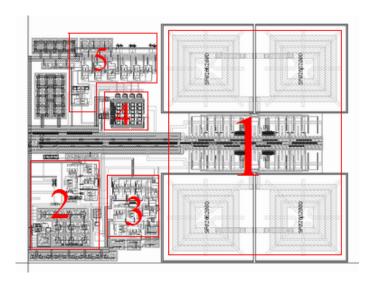

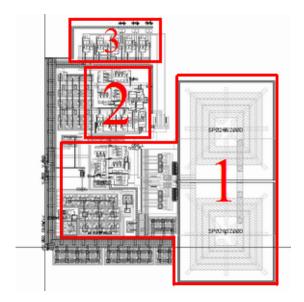

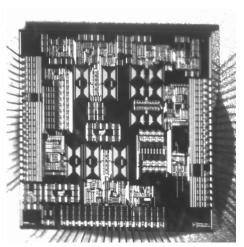

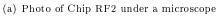

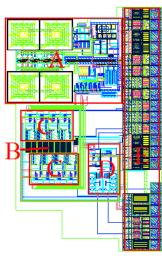

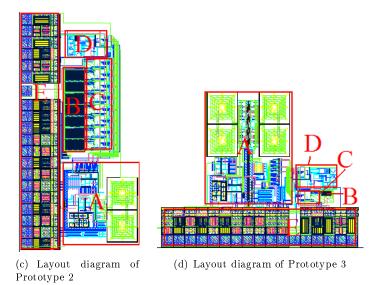

| 12.1  | Chip RF2: Photo and layout diagrams                                         | 170 |

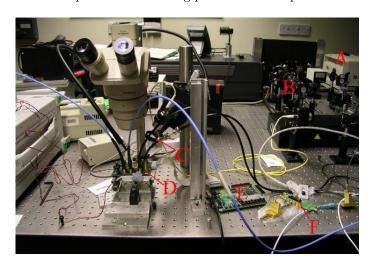

| 12.2  | Testing platform for Chip RF2                                               | 171 |

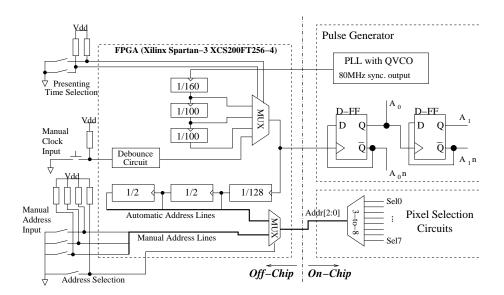

| 12.3  | Off-chip logic used for chip-testing                                        | 173 |

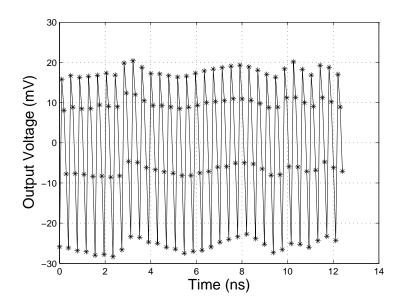

| 12.4  | Dark output of <i>Prototype 1</i>                                           | 175 |

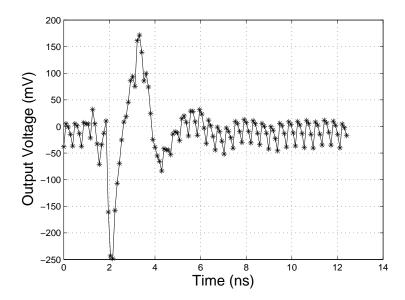

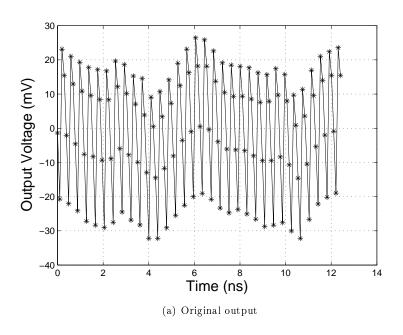

| 12.5  | Original output of $Prototype\ 1$ when pulse laser is applied               | 176 |

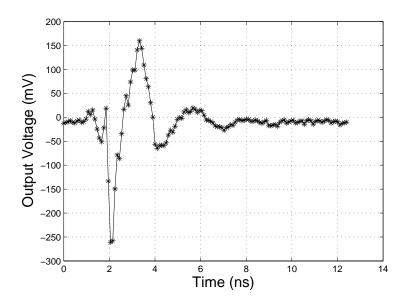

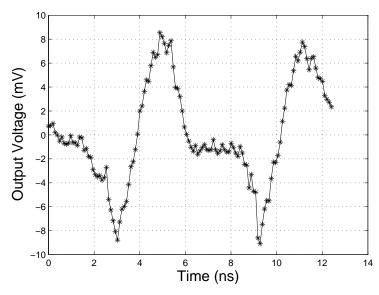

| 12.6  | Processed output of <i>Prototype 1</i> by removing system error and         |     |

|       | dark noise                                                                  | 177 |

| 12.7  | Leakage current from the N-well-P-sub junction                              | 178 |

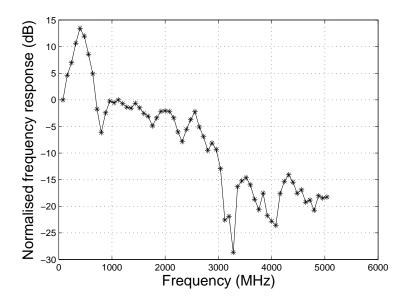

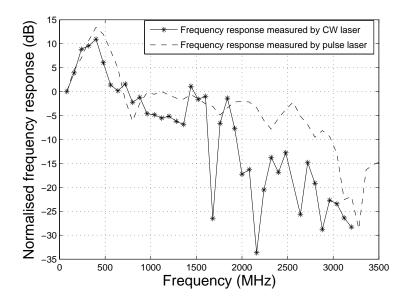

| 12.8  | Frequency response of the DAQ in <i>Prototype 1</i>                         | 179 |

| 12.9  | Waveform of signal $f=2f_0$                                                 | 180 |

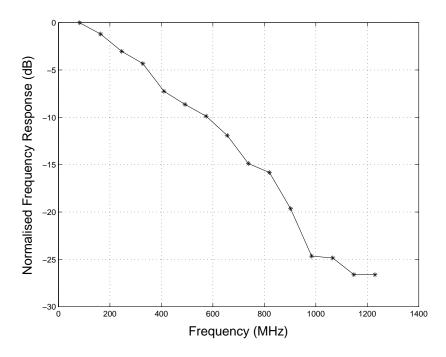

| 12.10 | Frequency Response of Circuit C in CW laser-input test                      | 181 |

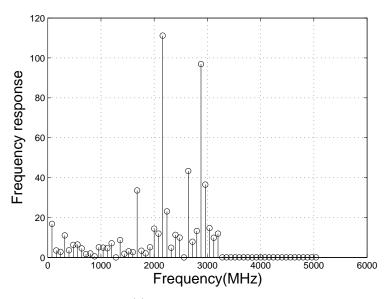

| 12.11 | Retrieved signal in frequency domain                                        | 184 |

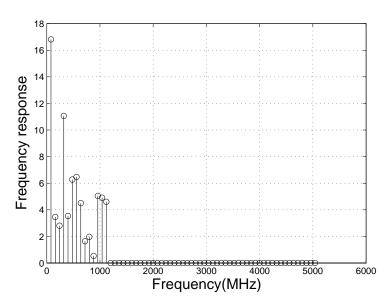

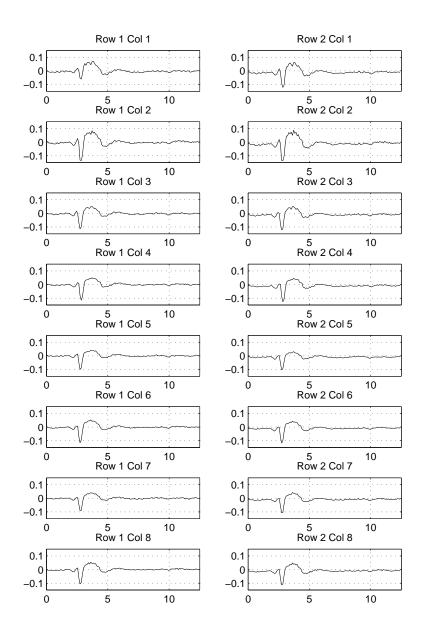

| 12.12 | Retrieved signal in time domain                                             | 185 |

| 12.13 | BPhoto: the laser is focusing to the top of the array in <i>Prototype 1</i> | 186 |

| LIST OF FIGURES                                                | XVIII |

|----------------------------------------------------------------|-------|

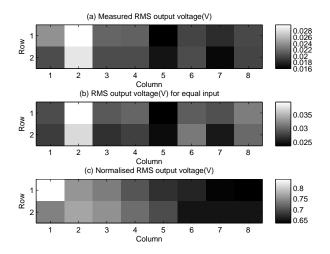

| 12.14Output waveforms of the pixel array                       | 187   |

| 12.15Relative light power received on the PD array             | 188   |

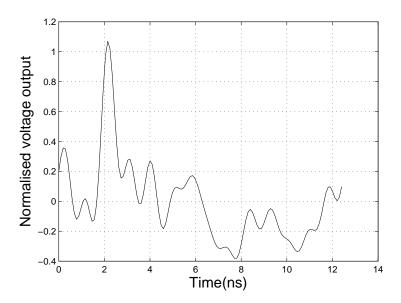

| 12.16Normalised frequency response of <i>Prototype 2</i>       | 190   |

| 13.1 Pixel circuit removing dark noise and 4-phase-clock error | 193   |

| 13.2 Output channel for the error-removing pixel circuits      | 194   |

| A.1 SCL D-type latch                                           | 205   |

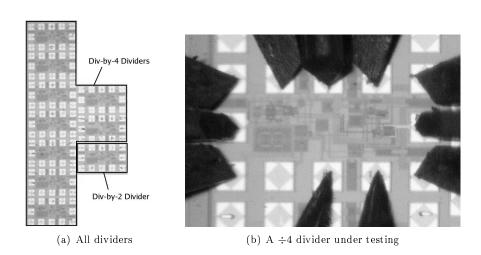

| A 2. Die photos of divided-by-four frequency dividers          | 208   |

# List of Tables

| 3.1  | Truth table of AOR gate                                             | 16  |

|------|---------------------------------------------------------------------|-----|

| 4.1  | Comparison of clock source solutions                                | 32  |

| 4.2  | Frequency range of QVCO                                             | 53  |

| 4.3  | Frequency range of the VCO for $2.6GS/s$ DAQ                        | 56  |

| 4.4  | Characteristics of the 3rd-order filter in the presented PLLs (sim- |     |

|      | ulation results)                                                    | 59  |

| 5.1  | Clock sources of Relative-Phase Clocks                              | 70  |

| 7.1  | Implementations of proposed Sub-Sampling SHA                        | 104 |

| 11.1 | Power Consumption of some key modules in the $10.5GS/s$ DAQ         | 156 |

| 12.1 | Circuit Specifications                                              | 169 |

# Part I

# Introduction to O-SAM and its DAQ system

#### Chapter 1

# Introduction to Optical

# Scanning Acoustic

# Microscopy

# 1.1 Optical Scanning Acoustic Microscopy (the optical part)

Optical Scanning Acoustic Microscopy (O-SAM) is a non-contact method to characterise the property of a material, or to detect hidden faults beneath the material surface.

In an O-SAM system, a series of periodical laser pulses, usually lasting from a few femto-seconds to several nano-seconds for each pulse, is applied on the material surface. When photons hit the surface, they are absorbed locally, and heat the surface. The heat is dissipated from the surface via bulk lattice vibrations (phonons) or surface vibrations (Surface Acoustic Waves (SAW)).

The amplitude and phase of the SAW contains information on the material

properties as well as the homogeneity of the materials. Consequently, if there are hidden defects beneath the surface, the propagation of the SAW will be affected. Therefore by imaging the SAW, these faults can be detected.

The SAW is generated by a high power pulse laser as described above, and the SAW field is detected by a second low power continuous-wave laser (the probe laser). The probe laser usually operates at a different wavelength to that of the pulse laser, so that it can be easily distinguished. As the surface vibrates, the reflected beam changes its direction back and forth slightly. The moving angles of the reflected beam are measured as the amplitudes of the SAW.

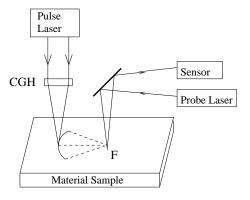

The Applied Optics group at the University of Nottingham have experience in building and using OSAM [1, 2, 3, 4, 5]. Figure 1.1 shows a simplified schematic of the general optical set-up of their OSAM system [1, 4].

Figure 1.1: Optical set-up of OSAM

As shown in the figure, the pulse laser is focused on an arc by a Computer Generated Hologram (CGH). Due the shape of the arc, the generated SAW concentrates on the point F. This is where the amplitude of the SAW reaches the maximum value, and it is also where the OSAM measurement is most interested. The probe laser hits the area around point F, and its reflection is detected by the sensor.

SAWs can be detected by measuring the changing angle of a reflected beam using techniques such as knife-edge detection [6], displacement interferometry [7], and photo-emf detection [8]. In the system developed in the University of

Nottingham, a modified knife-edge detector is used, which keeps the simplicity of the original knife-edge technique and improves the energy efficiency [4]. This detecting method involves a pair of differential photo-diodes, while other methods usually use single-ended photo-diodes.

Sometimes the density of the material sample is not uniform, or there are hidden faults in the sample. In these cases, the SAW cannot focus on the point F. Therefore the vibration on the area around the point F has to be thoroughly scanned by the probe laser and the detector. A more effective way to do this is by using a sensor array[5]. In this work [5], a 1-D differential sensor array, which is effectively a  $2 \times 16$  photo-diode array, was designed to detect the SAW.

# 1.2 Data Acquisition (DAQ) system for O-SAM (the electronic part)

#### 1.2.1 Detecting picosecond vibration

The high power pulse laser used to generate the SAW has a repeating frequency of approximately 82MHz. Therefore the SAW generated on the surface of the sample will contain harmonics of this frequency. Based on this feature, Sharples [4] designed an electronic sensor system with the lock-in detection technique. Initial research was concentrated on using the fundamental harmonic, i.e. 82MHz. Later experiments also used higher order harmonics up to several hundred megahertz. The limitation of his system is the bandwidth of the photon detection circuits.

However, some optical experiments without involving electronic circuits reveals that the SAW contains picosecond-range vibrations [9], i.e. at least several gigahertz. But compared to electronic circuits, optical devices are usually more bulky and expensive. Measuring electronically gives possibility of making a portable instrument, which would be more usable, convenient, and low-cost.

Therefore, a faster electronic detection system is naturally in demand. If faster circuits are used, higher frequency harmonics can be detected. The higher frequency harmonics have smaller wavelengths, and consequently the resolution of the imaging system will be better.

#### 1.2.2 Design targets

The aim of this thesis is to design an ultra-fast Data-AcQuisition (DAQ) system to measure the SAWs in O-SAM. It converts the optical signal (the reflecting probe laser) to an electronic signal, and then digitises it. A photo-diode array is included in this DAQ for the convenience of measurement.

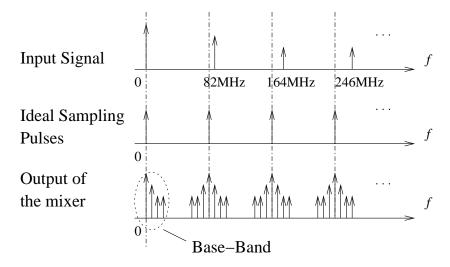

The optical input has a repeating period equal to the laser pulse repetitive frequency, i.e. 82MHz, and harmonics up to at least several gigahertz. The presented DAQ system was designed to capture the signal in time domain. The amplitudes and phases of the signal harmonics could be obtained by Fourier Transforming the obtained signal. The desired sampling rate of this system is 10GSample/s, therefore it should be able to detect the frequency information up to 5GHz.

The circuit was implemented on-chip so that making a low-cost portable instrument would be possible. The fabrication process used here was AMS C35, a  $0.35\mu m$  standard CMOS process with 4 layers of metal and 2 layers of polysilicon.

The SAW will contain frequency information greater than 5GHz. But it should noted that the 10GS/s sampling rate is very close to the performance limitation of the AMS C35 process. The insights into the design methodology will be invaluable when designing similar circuits in a more advanced fabrication process to achieve a higher sampling rate.

#### 1.3 Thesis organization

This thesis is divided into 6 parts.

Part I (Chapter 1 and 2) is a brief introduction to the DAQ system. Chapter 1 gives the background knowledge of OSAM, while Chapter 2 briefly presents the architecture of the DAQ and the design objectives.

Part II (Chapter 3~5) describes one key module of the DAQ, the clock source. The background introduction is given in Chapter 3. Chapter 4 presents the clock synthesiser, a 2.624GHz PLL with 4-phase outputs. Chapter 5 describes the pulse generator based on that PLL, which is used to drive the sampler.

Part III (Chapter 6~9) presents the other key module of the DAQ, the Sub-Sampling SHA (Sample-and-Hold Amplifier). Again, the first chapter (Chapter6) contains the background introduction. Chapter 7 presents the core circuit of the Sub-Sampling SHA, while its peripheral modules for error-correction are described in Chapter 8. Chapter 9 discusses the noise issues of the sampler.

Part IV (Chapter 10 and 11) is focused on the DAQ system itself. In Chapter 10, the front-end circuits, which are based on Mexiong Li's circuits, are introduced. Chapter 11 presents the detailed structure of the DAQ for OSAM sensor array.

Part V gives the measurement results (Chapter 12), and discusses the current issues and possible solutions (Chapter 13). The thesis is summarised in Chapter 14.

Part VI is the appendix.

#### Chapter 2

### System Architecture

#### 2.1 Structure and function description

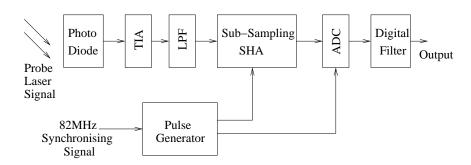

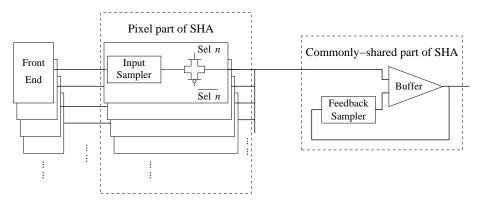

Figure 2.1: Architecture of DAQ system for OSAM

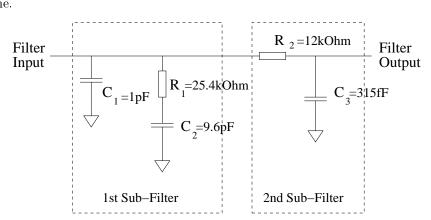

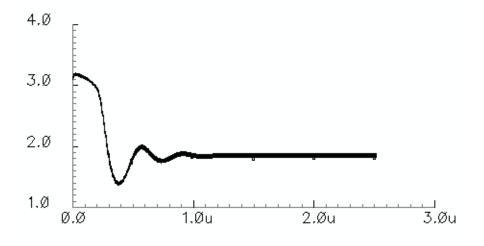

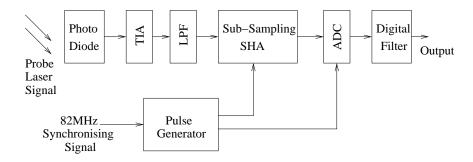

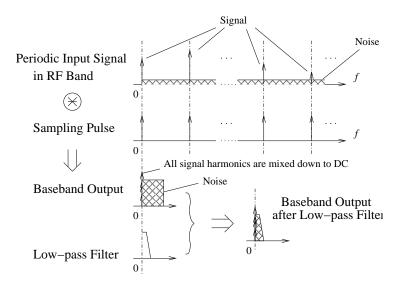

A brief architecture of the presented DAQ system for OSAM is shown in Figure 2.1. As shown in the figure, the Probe Laser signal is detected by the photodiode and amplified by a Trans-Impedance Amplifier (TIA). The output of the TIA is fed to a low-pass filter (LPF), so that any frequencies higher than half of the sampling rate are eliminated.

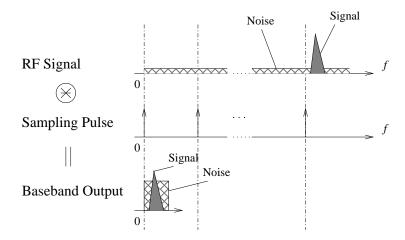

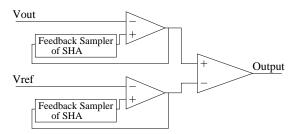

The Sub-Sampling Sample-and-Hold Amplifier (SHA) is the core module of the DAQ system. It samples the RF-band signal from the LPF, and transforms its spectrum down to a very low frequency range. Because of its frequency transfer ability, Sub-Sampling SHAs are sometimes termed Sub-Sampling Mixers.

The output of the Sub-Sampling SHA is digitised by a low-frequency A/D converter (ADC). The digital filter after the ADC is applied to compensate the distortion caused by the Sub-Sampling SHA.

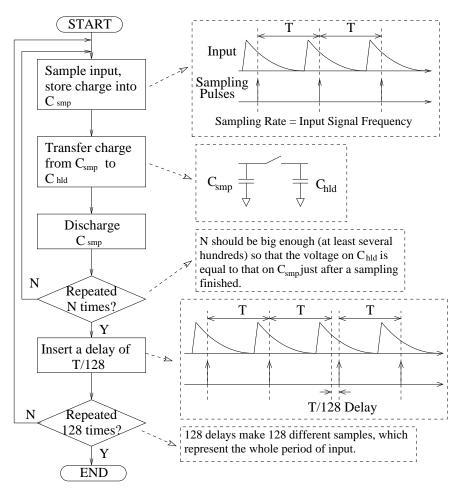

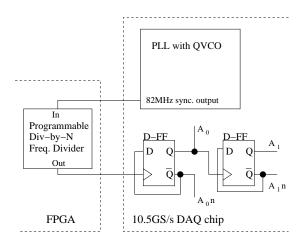

The pulse generator provides the control pulses for the Sub-Sampling SHA, and also acts as the central control unit of the system. It is based on a 2.624GHz PLL, which uses the electric synchronising signal from the pulse laser source as the reference signal. The PLL generates the clock signals in 4 evenly-divided phases. Therefore the minimum phase difference among the clocks is 1/4 of their period. This is equivalent to a clock signal at 10.496GHz, which are exploited to provide the required sampling signals.

Figure 2.1 illustrates the data acquisition of one photo-diode pixel only. The presented DAQ system is designed for a photo-diode array, and details of the array architecture are given in Chapter 11.

#### 2.2 Thesis objectives

In the presented DAQ system, the front-end modules (photo-diode, TIA, and LPF) are based on the topology of Li's design [10, 11], which is described in Chapter 10.

The low-frequency modules, i.e. the ADC and the digital filter, are currently offchip in order to shorten the design period. As they are not high-speed circuits, these modules can be easily implemented by existing mature technologies. They will be integrated into the on-chip system in the future prototypes.

This thesis is mainly focused on two key modules, the pulse generator and the Sub-Sampling SHA, which are presented in detail in Part II and Part III respectively.

The thesis is written in the structural order, i.e. the clock source first, then the SHA, and finally the DAQ. However, the time line of the design procedure was

actually:

PLL in the pulse generator  $\rightarrow$  Sub-Sampling SHA  $\rightarrow$ The pulse generator  $\rightarrow$  DAQ

The 4-phase output from the PLL makes the 10GS/s sampling possible whilst using a lower clock frequency. If a single phase output was used, a clock frequency of 10GHz would be required, and the design would not be achievable in the low cost AMS C35 process.

The ultra-fast Sub-Sampling SHA was designed to use the 4-phase clock source, and the whole pulse generator was tailored to satisfy the requirement of the control pulses for the Sub-Sampling SHA. Finally, the architecture of the whole DAQ was basically determined by the structure and features of the Sub-Sampling SHA and the pulse generator.

### Part II

# Clock Source and Pulse Generator

To achieve the required 10GS/s sampling rate, the most basic requirement is a clock operating at a frequency of more than 10GHz. However, this frequency is beyond the performance that the  $0.35\mu m$  CMOS process can deliver. Alternatively, a slower multiple clock source with the equivalent frequency information can be used to implement this function as well.

Part II presents such a clock source, and a pulse generator designated for the DAQ system for OSAM. The clock source is synchronised with the pulse laser via a PLL, and provides a multi-phase output which can be considered as the replacement of the 10GHz clock. The pulse generator circuit uses these clock signals to control the DAQ system, i.e. it provides the essential control signals for the Sub-Sampling SHA.

Chapter 3 introduces the background knowledge of clock synthesisers. Chapter 4 discusses the possible solutions to the DAQ for the OSAM firstly, then presents the designed clock source, a 2.624GHz PLL with quadrature outputs. Based on this clock source, the pulse generator is presented in Chapter 5.

#### Chapter 3

# Introduction to On-Chip

## Clock Synthesiser

This chapter introduces two commonly used techniques for clock synthesisers, the Phase-Locked Loop and the Delay-Locked Loop. Some methods for quadrature signal generation are also discussed in this chapter, as the multi-phase output is required for the DAQ system.

#### 3.1 Phase-Locked Loop (PLL)

#### 3.1.1 A brief history of PLL

The idea of PLL was firstly published by de Bellescize in 1932 [12]. This technique was mainly used for synchronous radio receptions at that time. Widespread use of the PLL began with TV receivers during the 1940's. PLLs were used to synchronise the screen sweeping oscillators to the sync pulses [13].

PLL circuits were quite complex at first, as they were implemented by discrete components. During 1960's, the development of integrated circuits rapidly

changed this situation. The availability of monolithic PLL IC created a considerable number of new applications which were previously limited by cost and complexity [13]. For a theoretical description of PLLs, references [14, 15, 16] should be consulted.

The availability of large-scale ICs after later 1970's brought strong interests in the implementation and design of digital PLL (DPLL), which is effectively a semi-analogue circuit [13]. The All-Digital PLL (ADPLL) and Software-Controlled PLL (SCPLL) were developed in 1980's [17]. These later two PLLs are more flexible than the traditional PLLs [16]. However, their operating speed is limited by the digital logic or software programmes, and so these PLLs are not suitable for high-speed applications. Consequently, analogue PLL and DPLL still play important roles in those applications [13].

Nowadays, PLL technology is widely used in communication, telemetry, instrumentation, motor control, etc. It is so important that there are still a great number of research papers published every year in this area.

#### 3.1.2 Principle and structure

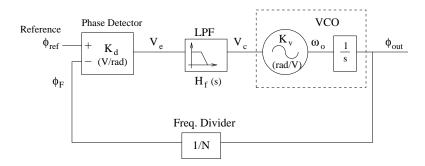

PLL is a device that makes a signal track another one (the reference) [18]. The frequency of that signal can be either equal to that of the reference, or a multiple of it. Their phases are synchronised, and that is the reason why it is called "phase-locked". PLL can also be considered as a feedback control system that automatically corrects the phase error between the signal and the reference. Figure 3.1 illustrates the general structure of a PLL.

The reference signal is represented by its phase,  $\phi_{ref}$ . It is compared to a feedback from the output,  $\phi_F$ , by a phase detector. The phase detector transfers the phase error into a voltage signal, i.e.

$$V_e = K_d(\phi_{ref} - \phi_F) \tag{3.1}$$

Figure 3.1: Structure of Phase-Locked Loop

This equation is only a behaviour model. The real situation is much more complicated, and is discussed in detail at Sub-Section 3.1.3 on the following page.

$V_e$  is fed into a Low-Pass Filter (LPF), whose transfer function is  $H_f(s)$ . The LPF is inserted to suppress the noise and high-frequency components in  $V_e$ . Consequently,

$$V_c = H_f(s)V_e = H_f(s)K_d(\phi_{ref} - \phi_F)$$

In ideal conditions, the output of the LPF  $V_c$  is a stable voltage signal, which can be used to control the VCO.

VCO (Voltage-Controlled Oscillator) is the module which generates the final output. Its oscillation frequency, or angular frequency, is determined by the control voltage  $V_c$ . In small-signal analysis, the VCO is usually considered as a linear element with the relationship  $\omega_o = K_v V_c$ .

However, it is the phase which is of interest, and so an extra block,  $\frac{1}{s}$ , is inserted in Figure 3.1, because the phase is essentially the integration of the angular frequency, i.e.

$$\phi_{out} = \frac{\omega_o}{s} = \frac{1}{s} K_v H_f(s) K_d(\phi_{ref} - \phi_F)$$

(3.2)

The Frequency Divider (FD) divides the output frequency by the number N, i.e.

$$\phi_F = \phi_{out}/N \tag{3.3}$$

FD usually appears in clock synthesizers, where the PLL is used to generate a clock whose frequency is N times of the reference. In the case that the output frequency is equal to that of the reference, N=1.

According to Equation (3.2) and (3.3), the transfer function of PLL can be derived:

$$\phi_{out} = \frac{1}{s} K_v H_f(s) K_d(\phi_{ref} - \phi_{out}/N)$$

$$\phi_{out} = \frac{N K_v K_d H_f(s)}{sN + K_v K_d H_f(s)} \phi_{ref}$$

(3.4)

Given enough time,  $\phi_{out} = N\phi_{ref}$ , and the PLL becomes stable and phase-locked.

#### 3.1.3 Phase detector and charge pump

As mentioned above, the phase detector is used to detect the phase difference between the reference  $\phi_{ref}$  and the feedback signal  $\phi_F$ . In Equation (3.1), its transfer function is described as a linear relationship. In reality, the output from a phase detector is a series of pulses which needs to be averaged to get the required phase error. The output also contains parasitic high frequency terms which need removing. Consequently a LPF at the output of the phase detector is always required.

There are a few different implementations of phase detectors, such as multiplier, XOR gate, and sequential logic.

#### Analogue multiplier phase detector

Analogue multipliers, such as Gilbert Cell, can be directly used as a phase detector in a PLL [19]. If the reference signal is  $V_1 \cos(\omega t + \phi_{ref})$  and the

feedback signal is  $V_2 \cos(\omega t + \phi_F)$ , the output of the Gilbert Cell is

$$V_e = \beta V_1 V_2 \cos(\omega t + \phi_{ref}) \cos(\omega t + \phi_F)$$

$$= \frac{1}{2} \beta V_1 V_2 \left(\cos(2\omega t + \phi_{ref} + \phi_F) + \cos(\phi_{ref} - \phi_F)\right)$$

where  $\beta$  is a constant depending on the property of the Gilbert Cell. The highfrequency component  $\cos(2\omega t + \phi_{ref} + \phi_F)$  will be "removed" by the LPF, and so the output voltage is given by

$$V_e \approx \frac{1}{2}\beta V_1 V_2 \cos(\phi_{ref} - \phi_F)$$

which is a DC voltage related to the phase difference.

#### XOR gate phase detector (Digital multiplier phase detector)

The XOR gate is a very simple digital implementation of phase detector. Its truth table is shown in Table 3.1. If the two input signals are considered as square waves, the XOR gate has a similar function as an analogue multiplier.

|     | A=0 | A=1 |

|-----|-----|-----|

| B=0 | 0   | 1   |

| B=1 | 1   | 0   |

Table 3.1: Truth table of XOR gate (Output = A XOR B)

If we define the logic "0" as -1, the logic "1" as 1, then

$$AXORB = -A \times B$$

which means the XOR gate acts as a digital multiplier.

#### Phase detector using sequential logic

The multiplier-based phase detectors, i.e. the analogue multiplier and the XOR gate, have been widely realized in discrete circuit systems, but are not popular

in high-performance on-chip systems. This is due to some of their shortcomings such as limited acquisition range, and the dilemma between phase error and response time [20].

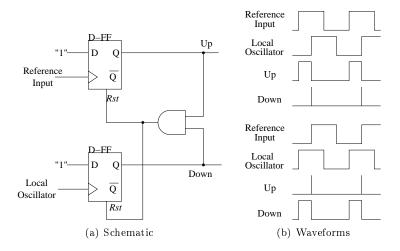

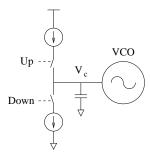

The widely-used solution in on-chip PLL is the sequential-logic-based phase detector. Figure 3.2(a) is a simple implementation of this type of phase detector [21, 22]. It is often termed Phase/Frequency Detector (PFD), as it can detect both phase difference and frequency difference [20].

Figure 3.2: Phase/Frequency Detector

Figure 3.2(b) illustrates the timing of PFD. If the reference input is ahead of the local oscillator, which is the feedback signal from the VCO through the FD, the "Up" signal is set. On the contrary, if the local oscillator is ahead of the reference, the "Down" signal is set. The pulse widths of the "Up" and "Down" are proportional to the phase difference  $(\phi_{ref} - \phi_F)$ .

## Charge Pump

PFD is often applied together with a charge pump, which is effectively a pair of controllable current sources [20]. Figure 3.3 illustrate how the charge pump works. In this figure, the LPF is replaced by a capacitor in order to simplify the explanation. When "Up" is active, the upper switch turns on and  $V_c$  goes up; When "Down" is active, the lower switch turns on and  $V_c$  goes down.

Figure 3.3: Charge Pump in PLL

# 3.1.4 Low-Pass Filter (LPF)

As mentioned above, the output of the phase detector or the charge pump is a series of pulses, which can not be directly used to control the VCO. So a LPF is inserted between the phase detector and the VCO to average the pulses.

When the frequency of the feedback signal is close to the reference frequency, the repetitive frequency of the output pulses of the phase detector is approximately equal to the reference frequency. Therefore the attenuation of the LPF at the reference frequency is an important parameter in PLL design, because these pulses always causes some spurs on the VCO¹. Obviously, a high-order LPF, e.g. a 4th-order or a 5th-order one, has a better performance on suppressing spurs than a low-order LPF.

However, a high-order LPF may cause the PLL to become unstable. If the transfer function of LPF  $H_f(s)$  is redefined as

$$H_f(s) = \frac{a(s)}{b(s)}$$

where a(s) and b(s) are polynomial expressions, the order of b(s) indicates how many poles the LPF transfer function has. Applying this definition to Equation (3.4) on page 15, then

$$\phi_{out} = \frac{NK_vK_da(s)}{sNb(s) + K_vK_da(s)}\phi_{ref}$$

<sup>&</sup>lt;sup>1</sup>A detailed description of these spurs is presented in Sub-Section 3.1.5 on Page 20.

Therefore the PLL will always have at least one pole, and always has one more pole than the LPF. This extra pole is due to the integration effect of the VCO, i.e.  $\phi_{out}$  is the integration of  $\omega_o$ .

Since in practical implementations, the PLL will always have more than one pole, the PLL is potentially unstable, especially when a high-order LPF is used in the PLL. Consequently, its stability must be carefully investigated.

# 3.1.5 Voltage-Controlled Oscillator (VCO)

The VCOs used in the PLLs are not different from those employed for other applications, such as modulation and automatic frequency control [18]. Four types of VCO commonly used are given in the order of decreasing stability, namely, voltage-controlled crystal oscillators (VCXO), resonator oscillators, RC multi-vibrators, and YIG tuned oscillators [14, 15].

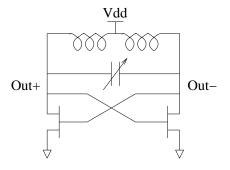

As crystals are not available on-chip, the resonator oscillators are often used in on-chip high-performance PLLs. This type of VCO has a tunable LC-tank, which is a passive circuit involving inductors (L) and capacitors (C). The LC-tank provides a resonant frequency, and this frequency is tunable via a variable capacitor (or sometimes a pair of variable capacitors). The frequently-used single-ended resonator VCOs includes Colpitts oscillators, Hartley oscillators, and Clapp oscillators [20, 23]. But the VCO to be used in the presented DAQ system is a differential VCO, which is often termed Negative-R VCO [23, 24].

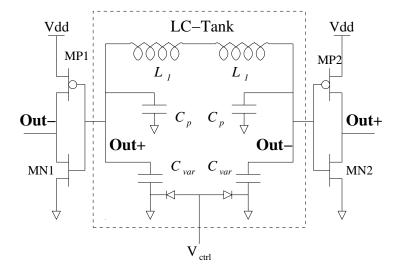

Figure 3.4: Differential Negative-R VCO

Figure 3.4 is a simplified differential Negative-R VCO. In this VCO, the cross-coupled transistors provide a negative resistance which is in parallel with the LC-tank. Therefore the resistive loss inside the LC-tank is compensated by the negative resistance, and the circuit oscillates at the resonant frequency of the LC-tank. Its differential structure naturally generates a pair of outputs which have 180° of phase difference.

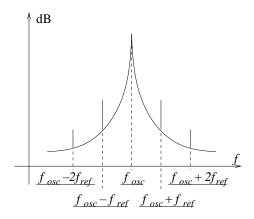

#### Spurs in VCO spectrum

As mentioned in Sub-Section 3.1.4 on page 18, the pulses from the phase detectors cause spurs in the VCO spectrum. This is because  $V_c$ , the control voltage of the VCO, is frequency-modulated into the VCO output. Any ripples on  $V_c$  will cause a small offset on the VCO oscillating frequency.

Typically, when the PLL is phase-locked, the output pulses from the phase detector has a frequency the same as the reference input,  $f_{ref}$ . Although these pulses are significantly suppressed by the LPF, they will still affect the spectrum of the VCO.

As for the PFD shown in Figure 3.2 on page 17, ideally, when the reference and the output of the FD are perfectly synchronised, the charge pump would not operate in any time, and its output is a stable DC voltage without any frequency information on  $f_{ref}$ . However in reality, the PMOS and NMOS transistors in the charge pump turn on for a very short time almost simultaneously when the rising edges of the input signals come. This results in a small ripple on the output of the charge pump. Naturally, the ripples have a repeating rate of  $f_{ref}$ .

These pulses or ripples on  $f_{ref}$  generate a few spurs in the spectrum of the VCO output. Figure 3.5 shows an example of a typical VCO spectrum. These spurs have a constant interval of  $f_{ref}$ , and the two spurs next to the main peak (the oscillating frequency) are  $f_{ref}$  away from it as well. In this case,  $f_{ref}$  is termed spur frequency. The interference on the spur frequency should be suppressed as

much as possible by the LPF, so that the spurs on the VCO output spectrum can be retained in the smallest amount.

Figure 3.5: Spectrum of VCO output

# 3.1.6 Frequency Divider (FD)

Frequency dividers are basically digital counters, which are usually available in design libraries, or can be easily synthesized from digital Flip-Flops.

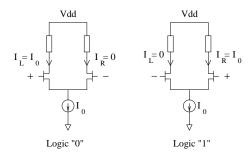

Figure 3.6: Current Mode Logic

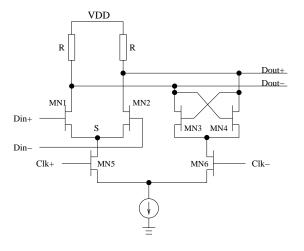

However in high-speed applications, the conventional CMOS Flip-Flops are not quick enough. Current-Mode-Logic (CML) circuits are widely used in this case [25, 26, 27]. CML circuits use differential amplifiers as the basic elements, because differential circuits are quicker than the normal logic circuits. As there are two branches in the circuit, the logic "1" and "0" are represented by which branch the current goes through, as shown in Figure 3.6. Figure 3.7 shows a CML T-type Flip-Flop, which can work as a divide-by-2 FD.

Figure 3.7: CML T-type Flip Flop

Over the last few years, there has been considerable research focusing on optimizing CML circuits [27, 28], especially those using CMOS fabrication processes [29, 30].

# 3.2 Delay-Locked Loop (DLL)

One major limitation of using PLL as a clock synthesizer is the phase noise. An alternative solution to it is the Delay-Locked Loop (DLL). Its phase noise does not depend on the integrated inductor quality factor, and the random timing error does not accumulate from cycle to cycle [31].

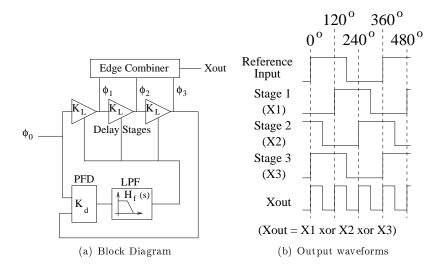

Figure 3.8: Delay-Locked Loop

Figure 3.8(a) is the block diagram of a 3-stage DLL. The delay time of the 3 delay stages is controlled by the voltage output of the LPF. When the circuit becomes stable, the phase of the 3rd delay stage  $\phi_3$  is synchronised with the input phase  $\phi_0$ , i.e.  $\phi_3 = \phi_0$ . Since the three delay stages are identical,  $\phi_1 = \phi_0 + 120^\circ$ , and  $\phi_2 = \phi_0 + 240^\circ$ . The edge combiner adds the output of the delay stages together, and obtains a signal in 3 times the frequency of the input, as shown in Figure 3.8(b).

The transfer function of DLL is

$$\phi_N = NK_L H_f(s) K_d(\phi_0 - \phi_N)$$

$$\phi_N = \frac{NK_L K_d H_f(s)}{1 + NK_L K_d H_f(s)} \phi_0$$

(3.5)

where  $K_L$  is the voltage-to-phase gain of each delay stage, and N is the number of stages. In Figure 3.8, N=3. Equation (3.5) has one less pole than Equation (3.4) on page 15. Therefore DLL is more likely to be stable than PLL.

# 3.3 Generation of quadrature signals

In the presented DAQ system, the clock source is required to produce 4-phase outputs, i.e.  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$  and  $270^{\circ}$ . This section introduces some methods to generate these quadrature signals.

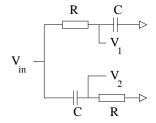

#### RC-CR network

Figure 3.9: RC-CR circuit

A simple quadrature technique is the RC-CR network [21], as shown in Figure 3.9.  $V_1$  and  $V_2$  always have a phase difference of 90°. The drawback of this circuit is that the amplitudes of  $V_1$  and  $V_2$  are usually unequal, except at the frequency  $1/2\pi RC$ .

#### Divide-by-2 FD

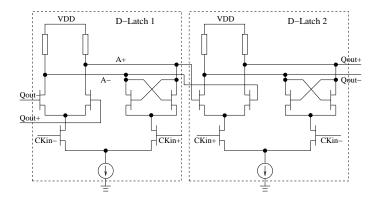

Another simple method is using a divide-by-2 FD. For example, the circuit in Figure 3.7 can achieve this function. When the duty cycle of CKin+/CKin-is 1:1, Qout+/Qout-is in quadrature with A+/A-.

However, CKin+/CKin- must be twice the required frequency. When that frequency is not achievable in the given fabrication process, this method is not applicable.

#### Quadrature VCO

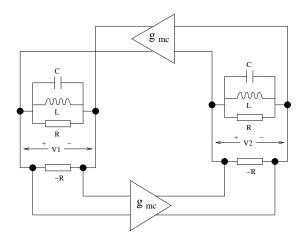

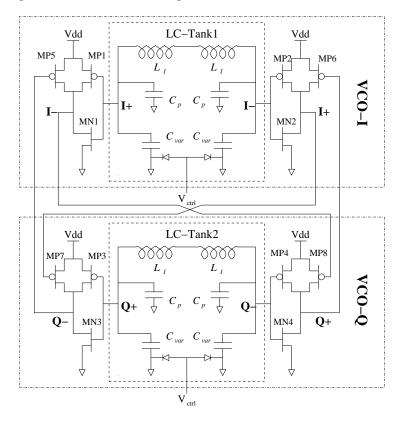

Quadrature Voltage-Controlled Oscillator (QVCO), which provides precise quadrature outputs, is based on two cross-coupled differential VCOs [32, 33]. The coupling structure forces these two VCOs oscillating in the same frequency and keeping a phase difference of 90°. Figure 3.10 sketches the general structure of a QVCO.

In this QVCO, two LC-tanks are driven by two negative resistors, which can be practically implemented by cross-coupled transistors. Two voltage-controlled current sources,  $g_{mc}$ , are applied to couple the oscillators. So

$$V_1(\frac{1}{sL} + sC) = V_2 g_{mc} \tag{3.6}$$

and

$$V_2(\frac{1}{sL} + sC) = -V_1 g_{mc} \tag{3.7}$$

Figure 3.10: Structure of QVCO

Multiplying (3.6) by (3.7) at both sides,

$$V_1 V_2 (\frac{1}{sL} + sC)^2 = -V_1 V_2 g_{mc}^2$$

If the circuit is oscillating,  $V_1V_2 \neq 0$ ,

$$\frac{1}{g_{mc}^2} (\frac{1}{sL} + sC)^2 = -1$$

therefore,

$$\frac{1}{g_{mc}}(\frac{1}{sL} + sC) = \pm j$$

and

$$V_1 = \pm jV_2$$

which means  $V_1$  and  $V_2$  are always in quadrature. The oscillating angular frequency is

$$\omega = \sqrt{\frac{1}{LC} + \frac{g_{mc}^2}{4C^2}} \mp \frac{g_{mc}}{2C}$$

There are two output frequencies, which corresponds to  $90^{\circ}$  and  $-90^{\circ}$  of phase differences between  $V_1$  and  $V_2$ . An ideal circuit as in Figure 3.10 provides these two frequencies simultaneously. In a real QVCO, these two frequencies have different feedback loop gains because of the parasitic resistances in the inductors, therefore only the one with the larger loop gain is generated in the

oscillator [34], i.e.

$$\begin{cases} V_1 = -jV_2 \\ \omega = \sqrt{\frac{1}{LC} + \frac{g_{mc}^2}{4C^2}} + \frac{g_{mc}}{2C} \end{cases}$$

In this case,  $V_1$  is 90° later than  $V_2$ .

## 4-Stage DLL

According to Section 3.2 on page 22, it is obvious that a 4-stage DLL can provide the required quadrature output.

# 3.4 Summary

This chapter introduced the fundamental theory of clock synthesisers. Two commonly used techniques for clock synthesisers, the Phase-Locked Loop and the Delay-Locked Loop, were described here. Some methods for quadrature signal generation are also discussed in this chapter, as the multi-phase output is required for the DAQ system.

# Chapter 4

# Design of Clock Synthesiser

# 4.1 Solutions to the clock source in the DAQ

# 4.1.1 System requirement

As mentioned in Part I, the design target of the presented DAQ is a sampling rate more than 10GSample/s. Thus a clock source which is more than 10GHz, or at least containing frequency information of more than 10GHz, is required.

For this clock source, there is a perfect ready-made clock reference, the stimulation pulse laser, which is the very source of all OSAM signals. The laser source usually provides an electrical output synchronised with the laser pulses. It can be used as the reference input of the clock source.

The 128th harmonic of the laser pulse repetitive frequency is slightly above 10GHz ( $82MHz \times 128 = 10.496GHz$ ), and so meets the specification. Moreover,  $128 = 2^7$ , is an easy number for frequency division, because only 7 divideby-2 frequency dividers are needed.

In the  $0.35\mu m$  standard CMOS process, AMS C35, the maximum oscillation frequency  $(f_{max})$  of NMOS transistors is below 50GHz, and the transient frequency  $(f_T)$  of NMOS is below 30GHz [35]. It is consequently impossible to

make a sequential circuit operating at 10GHz in this process. In reality, amplifiers can not reach a bandwidth more than 6GHz even using inductors for shunt-peaking [11]. Amplifiers are always needed to buffer the signals and clocks, and inductors occupy significantly larger chip areas than any other components. (The smallest one in AMS C35 process is more than  $6 \times 10^4 \mu m^2$ , while most transistors are less than  $100\mu m^2$ ). Moreover, the RF SPICE models provided by the foundry are only valid up to 6GHz[35], which also indicates that circuits operating at more than 6GHz are not realistic.

Therefore, the only way to overcome this limitation is to use multiple clocks operating at a lower frequency, rather than a single direct 10GHz clock. For example, one option could be a 5.248GHz clock  $(82MHz \times 64)$  with two output signals at different phases, 0° and  $180^{\circ}$ . The time difference between these two signals is half of their period, i.e.  $1/(2 \times 5.248GHz)$ . Similarly, a 2.624GHz clock  $(82MHz \times 32)$  with 0°, 90°,  $180^{\circ}$ , and  $270^{\circ}$  output, or a 3.444GHz clock  $(82MHz \times 42)$  with 0°,  $120^{\circ}$ , and  $240^{\circ}$  output<sup>1</sup>, are also applicable.

Ideally, the number of inductors need to be minimised, and so the lower clock frequency was chosen. As mentioned above, those high frequency amplifiers need inductors to boost their bandwidth, while inductors occupy large chip areas. This bandwidth-boost method is not suitable for a sensor array, as every pixel has to have several inductors to achieve the performance, and this would make the total chip area alarmingly huge. So inductor-less circuits are preferred for our application, i.e. the circuit bandwidth has to be reduced further. Additionally, if considering the simplicity of the frequency dividers, the 2.624GHz clock with 4-phase output is the most suitable choice.

# 4.1.2 Clock source solutions

Once the clock frequency has been chosen, there are two possible solutions to generate the 4-phase clock signals.

$<sup>^1 {\</sup>rm In}$  this case, the highest frequency achieved is the 126th harmonic (42  $\times$  3 = 126) of the fundamental frequency, 10.332 GHz.

## Solution 1: PLL with QVCO

The first solution is a 2.624GHz PLL with a QVCO, which is able to generate the required 4-phase output (0°, 90°, 180°, and 270°). Figure 4.1 illustrates the structure of the clock source. The PLL locks with the 82MHz synchronising signal, and provides the  $\times 32$  frequency output, i.e. 2.624GHz. VCO-I and VCO-Q are cross coupled so that their outputs are exactly in quadrature.

Figure 4.1: Clock source solution 1: PLL with QVCO

## Solution 2: PLL followed by DLL

The second solution is shown in Figure 4.2. Firstly, a normal  $\times 32$  PLL provides the 2.624GHz clock. Then a 4-stage DLL is applied to generate the 4 phases,  $0^{\circ}$ ,  $90^{\circ}$ ,  $180^{\circ}$ , and  $270^{\circ}$ .

Figure 4.2: Clock source solution 2: PLL followed by a DLL

### 4.1.3 Solution comparison

#### Chip area

A VCO requires an LC-tank, which contains at least one inductor, so the VCO will require a large chip area. Since the QVCO is essentially two cross-coupled VCOs, its chip area is approximately double. *Solution 1* has a QVCO, while the *Solution 2* has a normal VCO only. The DLL contains no inductors, and therefore needs much less chip area.

#### Power consumption

VCO is also a power-hungry circuit, and so the QVCO will have approximately double the power consumption of a single VCO. On the other hand, DLL contains several buffers operating at 2.624GHz. These high-frequency buffers are also power-consuming. So both of the two solutions need lots of power.

#### Responding time

Solution 1 has only one feedback loop, the PLL. But Solution 2 has two feedback loops, the PLL and the DLL. As a result, the responding time of the Solution 1 is faster than Solution 2.

## Signal degradation

In DLL design, it is very important to maintain the signal level throughout all the delay stages [31]. Otherwise, the signal going through the delay stages will degrade, i.e. the voltage swing would get smaller and smaller after every stage. This results in a serious problem for DLL, as the voltage swing affects the delay time of the stage. If the delay stages have different voltage swings, they have different delay times. Consequently, their output phases are no longer 90°, 180°,

270°, and 0°, but four unevenly-divided phases. The later stages provide less delay than its previous stages, for example, the output phases can be something like 93°, 184°, 273°, and 0° from the first stage to the last stage. The phase difference provided by each stage in this case is not 90°, but 93°, 91°, 89° and 87°, respectively. This is merely an example, and the real situation can be dramatically worse if signal degradation is obvious.

To overcome this problem, each delay stage must have enough gain and bandwidth to regenerate the input signal in the required delay time, namely

$$1/82MHz/32/4 = 95.3ps$$

Consequently, 95.3ps after the input changes, the output of the buffer amplifier must be no smaller than that of the input. This requirement is similar to the bandwidth requirement for a given rise/fall time for signal integrity. Accordingly, the bandwidth can be estimated from

$$BW = \frac{0.35}{RT}$$

where BW is the required bandwidth, RT is the rise (or fall) time of the signal [36]. The rising time here is defined as from 10% of the desired change to 90% of it. Therefore the bandwidth of the delay stage in our DLL can be estimated as

$$BW \approx \frac{0.35}{95.3ps \times 0.8} = 4.6GHz$$

This bandwidth is almost impossible to achieve without inductors in our given  $0.35\mu m$  CMOS process. Even if each stage contains just one inductor, the total of 4 inductors would make the DLL circuit much larger than the PLL, which has only one or two inductors.

Not like Solution 2, Solution 1 uses the QVCO to provide quadrature signals. The two VCOs inside the QVCO generate the phase output by themselves. Therefore the signal degradation is not an issue to QVCO.

#### Summary of comparison

Table 4.1 summarises the characteristics of the two solutions for the clock source. As shown in the table, the "PLL+DLL" solution is more economical as it needs less chip area. The "PLL with QVCO" solution is more functional, although one of its features, the responding time, is unimportant to the application.

|                    | Solution 1:   | Solution 2:             |

|--------------------|---------------|-------------------------|

|                    | PLL with QVCO | PLL+DLL                 |

| Chip area          | Big           | Relatively small        |

| Power Consumption  | High          | High                    |

| Responding time    | Short         | Long                    |

|                    |               | Severe, can be          |

| Signal degradation | Not a problem | overcome by sacrificing |

|                    |               | chip area               |

Table 4.1: Comparison of clock source solutions

However, to overcome signal degradation, the "PLL+DLL" solution has to sacrifice even more chip area than the other solution. This makes "PLL with QVCO" the more reliable and suitable solution.

Therefore, the "PLL with QVCO" solution is selected as the clock source for the proposed DAQ system design, and its structure is shown in Figure 4.1 on page 29. The sub-modules of the clock source are described in detail in the following sections.

In Section 7.7 on page 102, it is mentioned that besides the 10.496GSample/s DAQ, another 2.624GSample/s DAQ circuit is also implemented. This circuit needs a 2.624GHz clock source without the multi-phase output. Therefore, only a normal PLL is required. Its structure is the same as the PLL part of the "PLL+DLL" solution (Figure 4.2 on page 29). Most of its sub-circuits (PD, LPF, FD) can share the same design as those in the "PLL with QVCO" solution, except the VCO, which is described in detail in Sub-Section 4.4.2.

# 4.2 Phase/Frequency Detector and charge pump

The Flip-Flop based Phase/Frequency Detector (PFD) is used as the phase detector in Figure 4.1 on page 29. Although an analogue multiplier or an XOR gate can also be used as the phase detector, it may cause a problem of nonconstant phase change.

In multiplier or XOR gate based PLLs, the control voltage for VCO is provided by LPF. The voltage of LPF results from the phase difference between the local oscillator and the reference input. When the environment parameters (such as the temperature) change, the characteristics of VCO may change. To keep the PLL operating at the same frequency, the control voltage needs to be changed as well. Therefore the phase difference between the local oscillator and the reference input should be changed.

As a result, the phase difference between the output clock (which provides the "local oscillator" signal) and the laser pulse (which provides the "reference" signal) is not a constant, but may change when the environment changes. Although the phase value is not a required parameter for the measurement, it is necessary to keep it constant for data alignment, i.e. the measured data from different tests can be precisely aligned for comparison. Therefore multiplier or XOR gate based phase detectors are not suitable for the application.

On the other hand, the PFD using sequential logic in Figure 3.2(a) on page 17 can guarantee the phase difference between the local oscillator and the reference is always fixed when PLL is stable, whatever the environment is.

The PFD in the presented PLL is shown in Figure 4.3 together with the charge pump. The PFD is slightly different to the theoretical diagram in Figure 3.2 on page 17.

In this circuit, an additional capacitor  $C_{ext}$  is inserted on the output of the AND gate in order to extend the reset signal, Rst. If  $C_{ext}$  was not included, the reset times of the two D-FFs would depend thoroughly on the parasitic

Figure 4.3: Implementation of PFD and charge pump

capacitance, and so the reset times of the two D-FF would be different. There is a possibility that one D-FF is instantly reset to zero, deactivating Rst, before the other D-FF can be reset.  $C_{ext}$  causes a delay on Rst so that it remains active for a short time after the first D-FF changes to zero. Therefore resetting both D-FFs is ensured.

The transistors in the charge pump (MP1 and MN1) are not ideal current source, but this issue does not affect the functionality of the PLL. The current provided by either MP1 or MN1 ranges approximately from 0.2mA to 0.4mA, when the transistor is in saturation region. In the following sections, the gain of the PFD and the charge pump  $(G_{PDCP})$  are considered as

$$G_{PDCP} = \frac{0.3mA}{2\pi}$$

for the system-level evaluation of the PLL.  $G_{PDCP} = \frac{0.4mA}{2\pi}$  is also used as the extreme condition for stability analysis, as this is where the PLL is most likely to be unstable.

# 4.3 Frequency divider (FD)

# 4.3.1 FD using Source-Coupled Logic

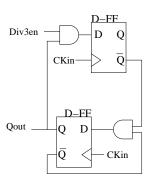

The FD in the presented PLL is a divide-by-32 divider. As  $32 = 2^5$ , it can be implemented by five divide-by-two dividers in cascade mode. The input frequency is 2.624GHz, which is divided to 82MHz by the FD. As CML has better performance in high frequency than CMOS logic, CML is used to implement the FD.

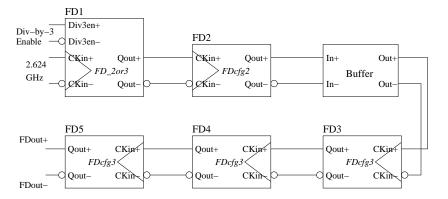

The structure of the  $\div 32$  divider is shown in Figure 4.4. Five  $\div 2$  dividers (FD1, FD2, ..., FD5) are connected in cascade mode.

Figure 4.4: CML frequency divider

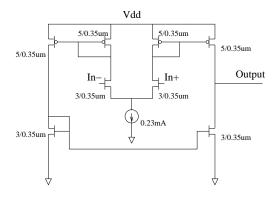

The circuit of each  $\div 2$  FD is shown in Figure 4.5. It is essentially a T-type Flip-Flop, which consists of 2 cross-coupled D-type latches. Sometimes the load resistors in the Flip-Flop are replaced by PMOS transistors, as their non-linear resistance is more functional for this application. However, transistors have larger parasitic capacitors than the linear poly-silicon resistors. To achieve a higher speed, the linear resistors are used here.

The five FDs have three different configurations on transistor sizes and load resistance, i.e. FDcfg1, FDcfg2 and FDcfg3 in the figure. These difference are

caused by trade-off between circuit speed and power consumption, The first two FDs (FD1 and FD2) need more speed as they operate in higher frequency. The latter three (FD3, FD4 and FD5) operate at lower frequency, so the performance requirement is eased. Therefore power-saving becomes a priority. The trade-off and optimisation is discussed in detail at Sub-Section 4.3.3.

Figure 4.5: Divide-by-2 frequency divider

A buffer circuit, as shown in Figure 4.6, is inserted between FD2 and FD3. It is needed because the voltage swing at the output of FD2 is not big enough to drive FD3.

Figure 4.6: Differential Buffer

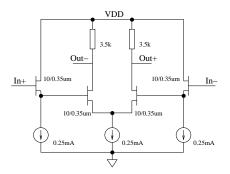

The differential-to-single-ended buffer is a simple push-pull Op-Amp, as shown in Figure 4.7 [37]. It transfers the differential output of FD5 into a single-ended logic signal which is compatible with normal CMOS logic. This is the signal which is fed into the "Local Oscillator" terminal of PFD.

Figure 4.7: Differential to single-ended buffer

# 4.3.2 Optimisation for frequency dividers

As shown in Figure 4.4 on page 35, the first frequency divider FD1 operates at the highest frequency, divider 2.624GHz to 1.312GHz. It has the most critical performance requirement than any of other FDs in the figure. In this subsection, the mechanism of the SCL Flip-Flop based FD is investigated, and a methodology to optimise the circuit performance is presented.

The CML Flip-Flop based FD consists of two D-type latches, which are connected in the master-slave mode as shown in Figure 4.5 on the preceding page. The toggle speed of the latches determines the maximum operating frequency of the Flip-flop. To fully understand the speed limitations of the FD, the mechanism of the latch is analysed. There are some literature on general optimising methods for CML [30, 29] in CMOS processes, and those for the bipolar processes[27], yet this sub-section presents an optimising technology specified for CML D-type latches.

#### Simplified transistor model

As a digital circuit, the latch operates in the large-signal mode, which is quite complicated for theoretical analysis. To simplify the calculation, a piecewise linear model is applied to the current-voltage characteristics of the MOS transistors, namely

$$I_{DS} = \begin{cases} G_m(V_{GS} - V_T) & \text{if } V_{GS} \ge V_T \\ 0 & \text{if } V_{GS} < V_T \end{cases}$$

(4.1)

where  $I_{DS}$  is the DC current from drain to source,  $V_{GS}$  is the DC voltage from gate to source,  $V_T$  is the effective threshold voltage, and  $G_m$  is the effective mean trans-conductance.  $V_{GS} < V_T$  is the cutoff region of the transistor, and  $V_{GS} \ge V_T$  is the combination of the triode and saturation regions.

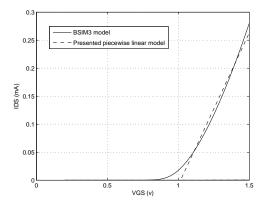

$V_T$  and  $G_m$  can be estimated from experimental measurements or simulations using a more accurate model, e.g. BSIM3[38]. In the proposed latch design, the values of  $V_T$  and  $G_m$  applied are those which have the minimum root-mean-square error to the BSIM3 model in the current-voltage curve. In this estimation,  $V_T$  is slightly larger than the values used in other transistor models, and  $G_m$  can be considered as an "average" value of the AC trans-conductance,  $g_m$ . Similar to  $g_m$ ,  $G_m$  can be adjusted by changing the transistor gate size. Figure 4.8 illustrates the comparison of an I-V curve based on the presented model and the one based on BSIM3 model in simulation.

Figure 4.8: Comparison of the presented piecewise linear model and BSIM3 model (Simulation condition:  $V_{SB}=1.5V,\,V_{DS}=1.5V,\,5\mu m/0.35\mu m$  NMOS transistor)

It must be noted that this piecewise linear model is inaccurate, and ignores the variety of  $V_{DS}$  as well. It is only suitable for design-parameter and performance

estimation in early-stage design. Accurate simulations on CAD software are necessary to fine-tune the design parameters.

#### Basic equations of latch toggling

Figure 4.9 shows a single D-type latch, which is half of the divide-by-2 FD.

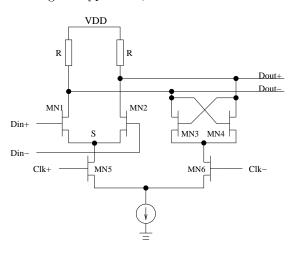

Figure 4.9: SCL D-type latch

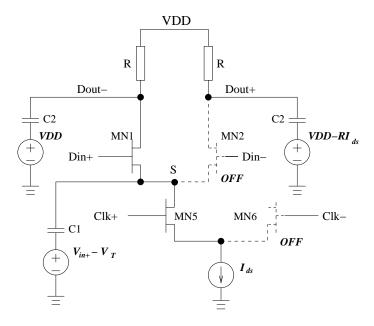

The circuit latches the data value when the clock input is low  $(V_{Clk+} < V_{Clk-})$ . Under this condition, transistor MN5 is off and transistor MN6 is on. The output of the latch (Dout+ / Dout-) remain constant, irrespective of the data input (Din+ / Din-), because of the feedback from the output to the input of the differential pair formed by transistors MN3 and MN4. When the clock goes high  $(V_{Clk+} > V_{Clk-})$ , MN6 turns off and MN5 turns on, and the output is determined by the data input (Din+ / Din-) through the differential pair MN1/MN2. Consequently the toggle speed of the latch depends on the response of the output ports to the input ports after the rising edge of the clock. This speed determines the maximum operating frequency of an SCL Flip-flop.

In the following analysis of the latch toggling, it is defined that the analogue voltages on the data input (Din+ / Din-) are  $V_{IN+}$  and  $V_{IN-}$ , respectively, and those on the data output (Dout+ / Dout-) are  $V_{OUT+}$  and  $V_{OUT-}$ , respectively.

It is assumed that the output logic state of the latch is low  $(V_{OUT+} < V_{OUT-})$ ,

and a logic-high signal has been applied to the input  $(V_{IN+} > V_{IN-})$  and settled before the rise edge of the clock, i.e. the input capacitors are fully charged. Thus the latch will start to toggle its logic state immediately after the clock turns high. To simplify the analysis, the transient effects from the data inputs are ignored  $(V_{IN+})$  and  $V_{IN-}$  remain constant through at the analysis).