# **5 GHz Optical Front End in** $0.35 \mu m$ **CMOS**

By Mengxiong Li, MSc.

Thesis submitted to The University of Nottingham for the degree of Doctor of Philosophy

Oct 2007

## ABSTRACT

With the advantages of low cost, low power consumption, high reliability and potential for large scale integration, CMOS monolithically integrated active pixel chips have significant application in optical sensing systems. The optical front end presented in this thesis will have application in Optical Scanning Acoustic Microscope System (O-SAM), which involves a totally non-contact method of acquiring images of the interaction between surface acoustic waves (SAWs) and a solid material to be characterized.

In this work, an ultra fast optical front-end using improved regulated cascade scheme is developed based on AMS  $0.35 \mu m$  CMOS technology. The receiver consists of an integrated photodiode, a transimpedance amplifier, a mixer, an IF amplifier and an output buffer. By treating the n-well in standard CMOS technology as a screening terminal to block the slow photo-generated bulk carriers and interdigitizing shallow p + junctions as the active region, the integrated photodiode operates up to 4.9 GHz with no process modification. Its responsivity was measured to be 0.016 A/W. With multi-inductive-series peaking technique, the improved ReGulated-Cascade (RGC) transimpedance amplifier achieves an experimentally measured -3dB bandwidth of more than 6 GHz and a transimpedance gain of 51 dB $\Omega$ , which is the fastest reported TIA in CMOS 0.35 $\mu m$  technology. The 5 GHz Gilbert cell mixer produces a conversion gain of 11 dB, which greatly minimized the noise contribution from the IF stage. The noise figure and input IIP<sub>3</sub> of the mixer were measured to be 15.7 dB and 1.5 dBm, respectively. The IF amplifier and output buffer pick up and further amplify the signal for post processing. The optical front end demonstrates a typical equivalent input noise current of 35  $pA/\sqrt{Hz}$  at 5 GHz, and a total transimpedance gain of 83 dB $\Omega$ while consuming a total current of 40 mA from 3.3 V power supply. The -3 dB bandwidth for the optical front end was measured to be 4.9 GHz. All the prototype chips, including the optical front end, and the individual circuits including the photodiode, TIA, mixer were probe-tested and all the measurements were taken with Anritsu VNA 37397D and Anritsu spectrum analyser MS2721A.

## Acknowledgments

I would like to thank Ian Harrison and Barrie Hayes Gill, my supervisors, for their guidance throughout my research work. I am very grateful to Barrie who, over the time of the research work, has constantly provided ideas, suggestions and much inspiration. For Ian, it is your brilliant insights and support that make this work possible, I owe you so much not only for your support on the research, but also for your support in my life, without reservation, like a friend.

I would like to express my thanks to the research staff in applied optics group in Electrical and Electronic Engineering Department, University of Nottingham for their support and cooperation on the work. Thanks also go to the many colleagues and technicians who have in one way or another been involved in my work.

Amongst my friends, I would like to thank Frank, Vinoth, Kudip and Fen for the happy time in the office. Especially I would like to thank Sheng, my deep friend in UK, for all you did for me I will always be grateful. For Ting, thank you so much for the happy time and your patience on the word processing.

Finally, my sincere thanks go to my family, and my deepest gratitude and love to my parents, my brother and my dear sister for their belief in me.

## **Acronyms and Abbreviations**

- ADS Advanced Design System

- AMS C35 Austria Micro Systems CMOS  $0.35\mu m$  process

- APD Avalanche Photodiode

- APS Active Pixel Sensor

- BER Bit Error Rate

- CCD Charge Coupled Device

- CB Common Base

- CG Common Gate

- CGH Computer Generated Hologram

- CMOS Complementary Metal Oxide Semiconductor

- CS Common Source

- D2S Differential to Single

- DCR Direct Conversion Receiver

- DFB Distributed Feedback

- DSB Double Side Band

- DUT Device Under Test

- EHP Electron Hole Pair

- ENR Excessive Noise Ratio

- FET Field Effect Transistor

- ICP Input 1-dB Compression Point

- IF Intermediate Frequency

- I/O Input Output

- G-S-G Ground Signal Ground

- LO Local Oscillator

- LRM Line Reflection Matched

- LA Limiting Amplifier

- MSM Metal Semiconductor Metal

- NA Numerical Angle

- NDT Non Destructive Test

- NF Noise Factor (Noise Figure)

- O-SAM Optical scanning Acoustic Microscopy

- PCB Printed Circuit Board

- PD Photodiode

- PIN P+ Insulator N+

- **RBW** Resolution Bandwidth

- RGC ReGulated Cascode

- RF Radio Frequency

- SAW Surface Acoustic Wave

- SiGe Silicon Germanium

- SML Spatial Modulated Light

- SOI Silicon On Insulator

- SOLT Short Open Load Through

- SSB Single Side Band

- TIA Transimpedance Amplifier

- VBW Video Bandwidth

- VCSEL Vertical Cavity Surface Emitting Laser

- VLSI Very Large Scale Integrated

- WG Wave Guide

# Contents

| 1 | Intr | oduction                               | 18 |

|---|------|----------------------------------------|----|

|   | 1.1  | Photoacoustic History                  | 19 |

|   | 1.2  | Physics Behind Photoacoustic           | 20 |

|   | 1.3  | Non-Destructive Test (NDT)             | 21 |

|   |      | 1.3.1 Flaw Detection                   | 21 |

|   |      | 1.3.2 Material Characterization        | 22 |

|   | 1.4  | O-SAM in University of Nottingham      | 23 |

| 2 | Pho  | todetector                             | 25 |

|   | 2.1  | Introduction                           | 25 |

|   | 2.2  | Principles of Photodetection           | 26 |

|   | 2.3  | Overview of High Speed Photodetectors  | 31 |

|   |      | 2.3.1 <i>p-i-n</i> Photodiode          | 32 |

|   |      | 2.3.2 MSM Photodiode                   | 33 |

|   |      | 2.3.3 Avalanche Photodiode             | 34 |

|   | 2.4  | Overview of CMOS Photodetector         | 36 |

|   | 2.5  | Photodetector in AMS $0.35 \mu m$ CMOS | 43 |

|   |      | 2.5.1 Introduction and calculation     | 43 |

|   |      | 2.5.2 Simulation                       | 47 |

|   |      | 2.5.3   | Implementation                               | 0 |

|---|------|---------|----------------------------------------------|---|

|   | 2.6  | Measu   | rement                                       | 3 |

|   |      | 2.6.1   | Laser source                                 | 3 |

|   |      | 2.6.2   | DC characterizations of PDs                  | 6 |

|   |      | 2.6.3   | High frequency characterizations of PDs 6    | 2 |

| 3 | Tran | isimped | ance Amplifier 6                             | 7 |

|   | 3.1  | Introdu | uction                                       | 7 |

|   | 3.2  | Overvi  | ew of the Transimpedance Amplifier 6         | 9 |

|   |      | 3.2.1   | Common-Gate TIA                              | 1 |

|   |      | 3.2.2   | Regulated Cascode TIA                        | 5 |

|   |      | 3.2.3   | Shunt-Shunt Feedback TIA                     | 7 |

|   |      | 3.2.4   | Calculations on a typical feedback TIA       | 3 |

|   | 3.3  | TIA in  | AMS $0.35\mu m$ CMOS                         | 0 |

|   |      | 3.3.1   | Small signal analysis                        | 1 |

|   |      | 3.3.2   | Inductive-series peaking                     | 6 |

|   |      | 3.3.3   | Noise analysis                               | 0 |

|   |      | 3.3.4   | Design consideration                         | 4 |

|   |      | 3.3.5   | Layout                                       | 6 |

|   | 3.4  | Measu   | rement                                       | 8 |

|   |      | 3.4.1   | Calibration for on wafer measurement         | 8 |

|   |      | 3.4.2   | Frequency response measurement of the TIA 11 | 9 |

|   |      | 3.4.3   | Noise measurement of the TIA                 | 4 |

| 4 | Mix | er       |                                                  | 129   |

|---|-----|----------|--------------------------------------------------|-------|

|   | 4.1 | Introdu  | uction                                           | . 129 |

|   |     | 4.1.1    | Mixing phenomena                                 | . 130 |

|   |     | 4.1.2    | Mixer topologies                                 | . 132 |

|   |     | 4.1.3    | Mixer performance parameters                     | . 137 |

|   | 4.2 | Gilber   | t Cell Mixer Analysis                            | . 140 |

|   | 4.3 | 5 GHz    | Mixer in AMS $0.35\mu m$ CMOS                    | . 147 |

|   |     | 4.3.1    | Optimization techniques in AMS $0.35 \mu m$ CMOS | . 147 |

|   |     | 4.3.2    | Matching network                                 | 150   |

|   |     | 4.3.3    | LO driver and D2S                                | 153   |

|   |     | 4.3.4    | Mixer core                                       | 158   |

|   | 4.4 | Measu    | rement                                           | . 166 |

|   |     | 4.4.1    | Mixer measurement set up                         | 166   |

|   |     | 4.4.2    | Conversion gain measurement                      | . 168 |

|   |     | 4.4.3    | Linearity and noise measurement                  | . 172 |

| 5 | Opt | ical Fro | nt end                                           | 177   |

|   | 5.1 | Review   | v of CMOS Optical Receiver                       | . 177 |

|   | 5.2 | Mixer    | based Optical Front-end                          | . 181 |

|   |     | 5.2.1    | System architecture                              | . 181 |

|   |     | 5.2.2    | PD and circuit design                            | . 183 |

|   |     | 5.2.3    | Measurement results                              | . 186 |

|   | 5.3 | TIA ba   | ased optical Front end                           | . 189 |

|   |     | 5.3.1    | System architecture                              | . 189 |

|   |     | 5.3.2    | Circuits and simulation results                  | . 190 |

|   |     | 5.3.3    | Measurement results                              | . 193 |

| 6 | Con | clusion  |                                                  | 200   |

# **List of Figures**

| 1.1 | Bell's plan for photophone[2]                                                                                                                                                                                                                                           | 20 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Photoacoustic generation                                                                                                                                                                                                                                                | 21 |

| 1.3 | Diagram of all-Optical Scanning Acoustic Microscopy (O-SAM)      [12]                                                                                                                                                                                                   | 24 |

| 2.1 | Optical absorption coefficients for various materials[45, 46]                                                                                                                                                                                                           | 27 |

| 2.2 | (a) PN junction as a photodiode (b) equivalent circuit for a p-n junction photodiode                                                                                                                                                                                    | 30 |

| 2.3 | <i>p-i-n</i> photodiode                                                                                                                                                                                                                                                 | 32 |

| 2.4 | MSM photodiode cross section and top view                                                                                                                                                                                                                               | 34 |

| 2.5 | Avalanche Photodiode                                                                                                                                                                                                                                                    | 35 |

| 2.6 | Silicon absorption length[44]                                                                                                                                                                                                                                           | 37 |

| 2.7 | Diffusion long tail                                                                                                                                                                                                                                                     | 38 |

| 2.8 | (a) simplified cross section of SiGe BiCMOS realization of NMOS, PMOS, and $n$ - $p$ - $n$ device. (b) photodiode in BiCMOS, where the N+ buried layer is utilized as screen terminal which blocks slow bulk carriers to high field region. (c) photodiode in CMOS SOI, |    |

|     | where the insulator layer (i.e. oxide) acts as the screen terminal                                                                                                                                                                                                      | 39 |

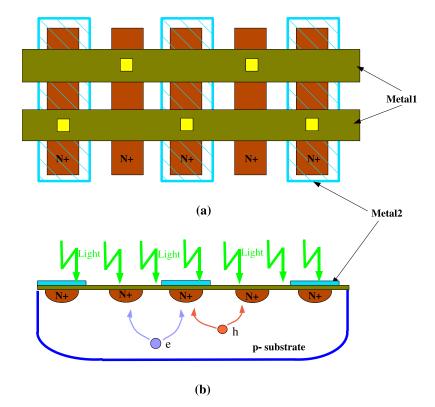

| 2.9  | Modulated Spatial Light Photodiode in CMOS (a) top view of              |      |

|------|-------------------------------------------------------------------------|------|

|      | SML photodiode, the $n$ + active region are alternatively exposed       |      |

|      | by the floating shading of the Metal 2. Metal 1 collects the pnotogener | ated |

|      | currents from the shaded $n$ + regions and exposed ones. (b) cross      |      |

|      | section of SML photodiode. The p- substrate contact (anode of           |      |

|      | the photodiode) are not shown here, which is generally connected        |      |

|      | to a fixed potential. The difference of the two cathodes gives the      |      |

|      | output of the photodiode                                                | 42   |

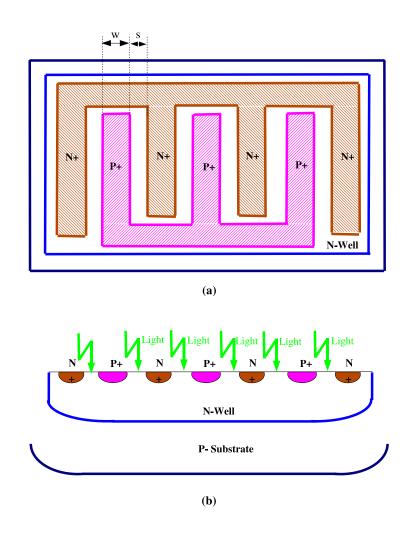

| 2.10 | Photodiode implemented in AMS C35 (a) top view of the interdigitate     | d    |

|      | photodiode (b) crossection of the photodiode.                           | 44   |

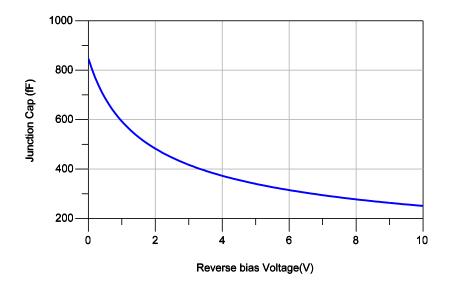

| 2.11 | Junction capacitance vs. reverse-bias voltage for the chosen CMOS       |      |

|      | technology (the effective area of the photodiode is $900  um^2$ )       | 47   |

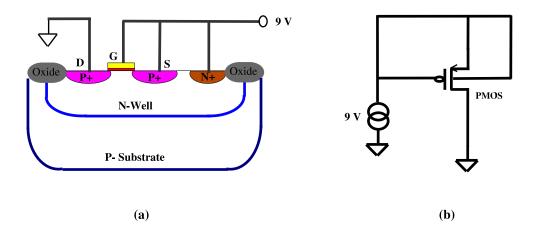

| 2.12 | Schematic for simulation (a) the cross section of PMOS transistor;      |      |

|      | (b) schematic for simulation of photodiode's parasitic junction         |      |

|      | capacitance modeled by a PMOS transistor                                | 48   |

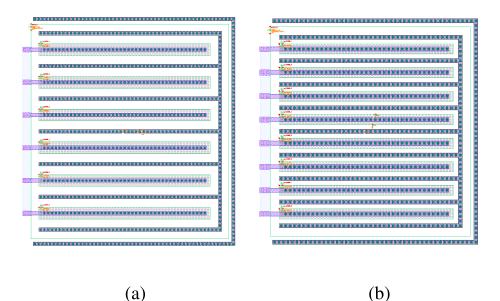

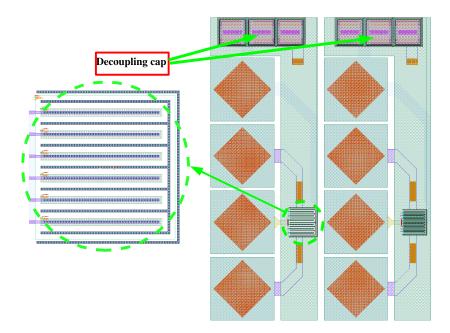

| 2.13 | Photodiodes layout in AMS C35 (a) version 1; (b) version 2              | 51   |

| 2.14 | Photodiode test circuits for the two versions. Photodiode are zoomed    |      |

|      | in left-sided. G-S-G pads are used here for cathode outputs of the      |      |

|      | photodiodes which give 50 $\Omega$ impedance match to measurement       |      |

|      | setup; the anodes are taken out by normal analog pads, with 3 $pf$      |      |

|      | on-chip decoupling capacitors.                                          | 52   |

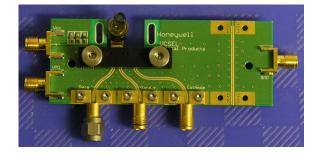

| 2.15 | Picture of the test board for laser diode HFE4080-32X-XBA               | 55   |

| 2.16 | Picture of the evaluation board for laser diode HFE6391-561             | 55   |

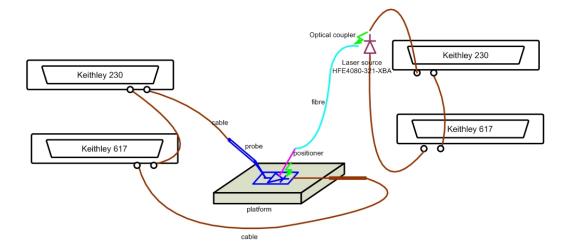

| 2.17 | Photodiode DC test set up                                               | 57   |

| 2.18 | Die micrograph of the photodiodes                                       | 57   |

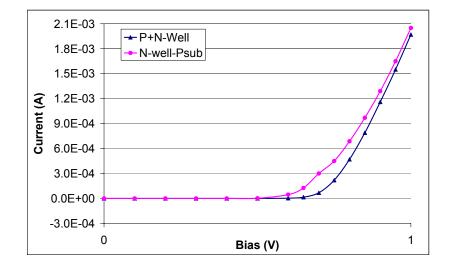

| 2.19 | I-V curves of the p+ nwell and nwell psub photodiode                    | 58   |

| 2.20 | Responsivity of PD1 with different reverse biased voltage applied       | 60   |

| 2.21 | Responsivity of PD2 with different reverse biased voltage applied       | 61   |

| 2.22 | Responsivity of nwell-psub photodiode with different reverse biased     |      |

|      | voltage applied                                                         | 61   |

| 2.23 | Photodiode high frequency response measurement set up                                                                                | 62 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

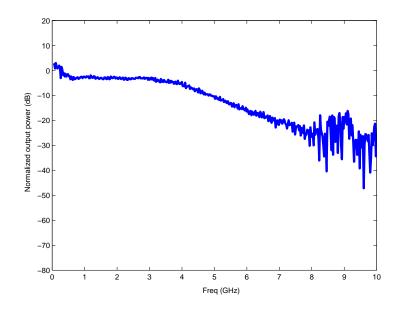

| 2.24 | Frequency response of PD1 with reverse biased voltage of 9 V                                                                         | 63 |

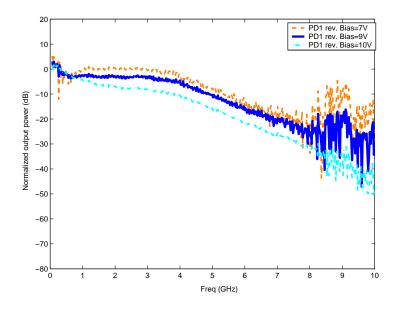

| 2.25 | Frequency response of PD1 with reverse biased voltage of 7 V, 9 V and 10 V                                                           | 64 |

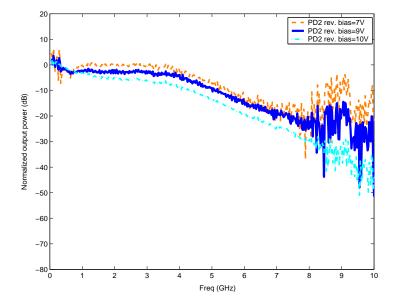

| 2.26 | Frequency response of PD2 with reverse biased voltage of 7 V, 9 V and 10 V.                                                          | 65 |

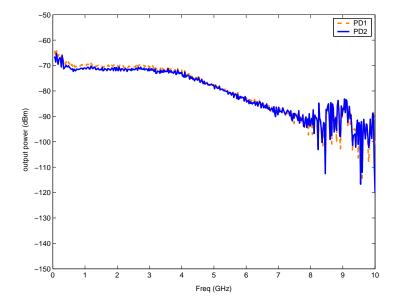

| 2.27 | Measured output power of both PD1 and PD2 at reverse biased voltage of 9 V, the RF input power is 3 dBm to laser source HFE6391-561. | 66 |

| 3.1  | Simple resistive optical front end                                                                                                   | 69 |

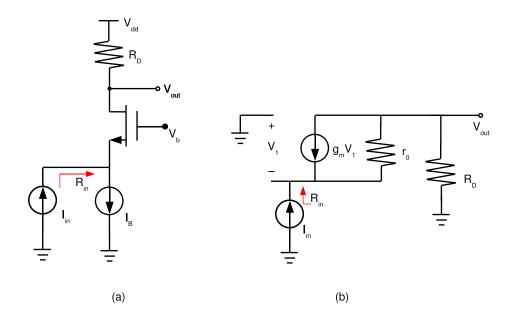

| 3.2  | Common-gate stage (a) schematic (b) small-signal equivalent circuit.                                                                 | 72 |

| 3.3  | (a) Common-gate stage with bias current source (b) equivalent circuit with noise sources                                             | 74 |

| 3.4  | Regulated cascode TIA input stage                                                                                                    | 76 |

| 3.5  | Shunt-shunt Feedback TIA (a) the simplified schematic with a feedback resistor (b) the equivalent circuit of (a) with noise sources  |    |

|      | added                                                                                                                                | 78 |

| 3.6  | Shunt-shunt Feedback TIA bandwidth                                                                                                   | 82 |

| 3.7  | Implementation of feedback TIA                                                                                                       | 84 |

| 3.8  | Equivalent small signal circuit of feedback TIA in Fig. 3.7 for calculating (a) input impedance (b) output impedance                 | 84 |

| 3.9  | Equivalent small signal circuit of feedback amplifier in Fig. 3.7 for calculating (a) transimpedance gain as a TIA (b) voltage gain  |    |

|      | as a broadband amplifier                                                                                                             | 86 |

| 3.10 | TIA schematic implemented in AMS C35                                                                                                 | 91 |

| 3.11 | Small signal equivalent circuit of RGC input stage                                                                                   | 92 |

| 3.12 | Small signal equivalent circuit of shunt-shunt feedback amplifier stage                                                              | 94 |

| 3.13 | Shunt-peaking (a) simplified shunt-peaking amplifier (b) model of shunt-peaking amplifier                                                                                                                                               | 97 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.14 | Small signal circuit of an amplifier with inductive-series peaking .                                                                                                                                                                    | 99 |

| 3.15 | Simulated gain of amplifier in Fig. 3.14 with different inductor values $(R_1 = 1\Omega, R_2 = \infty, C_1 = C_2 = 0.5F)$                                                                                                               | 00 |

| 3.16 | Noise equivalent circuit of the TIA (the input equivalent noise current of the shunt feedback amplifier is referred as $\overline{i_{eq,fb}}$ ) 1                                                                                       | 01 |

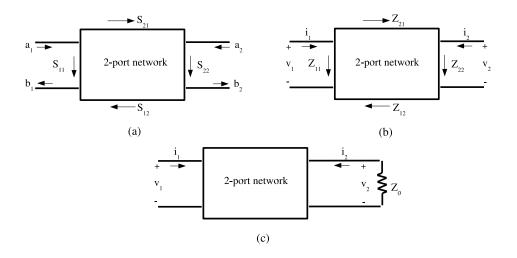

| 3.17 | 2-port network parameters (a) <i>S</i> parameters (b) <i>Z</i> parameters (c) <i>Z</i> parameters for calculating transimpedance gain $Z_T$                                                                                             | 05 |

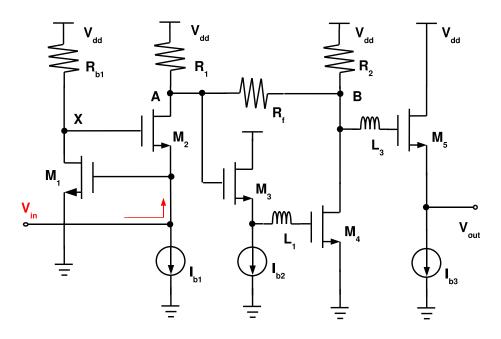

| 3.18 | TIA implemented in AMS C35 with inductor-series peaking 1                                                                                                                                                                               | 08 |

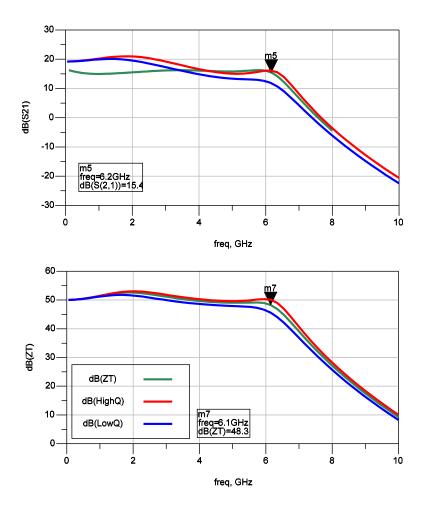

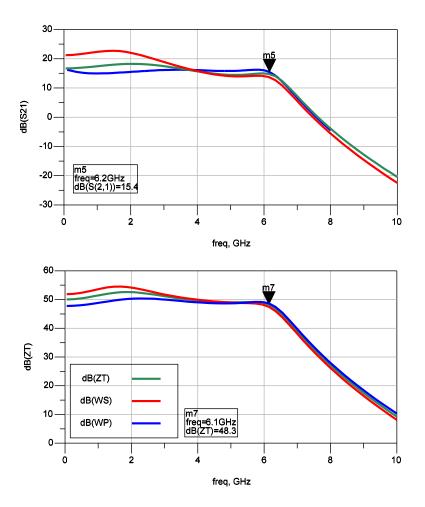

| 3.19 | Simulation results of TIA with inductor-series peaking and without inductor-series peaking                                                                                                                                              | 10 |

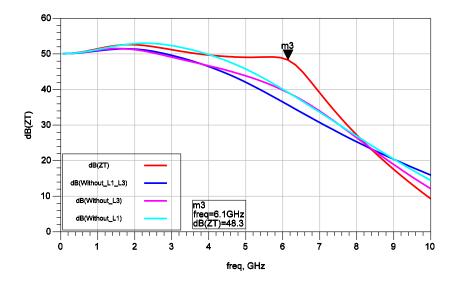

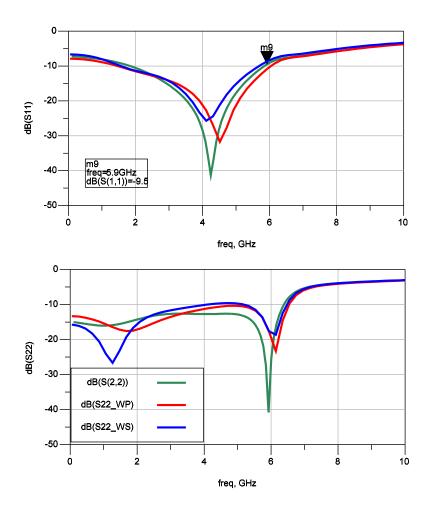

| 3.20 | Simulation results of $S_{11}$ and $S_{22}$ of the TIA in AMS C35 with different inductor models                                                                                                                                        | 12 |

| 3.21 | Simulation results of $S_{21}$ and $Z_T$ of the TIA in AMS C35 with different inductor models                                                                                                                                           | 13 |

| 3.22 | Simulation results of $S_{11}$ and $S_{22}$ of the TIA in AMS C35 with different resistor models $\ldots \ldots \ldots$ | 14 |

| 3.23 | Simulation results of $S_{21}$ and $Z_T$ of the TIA in AMS C35 with different resistor models                                                                                                                                           | 15 |

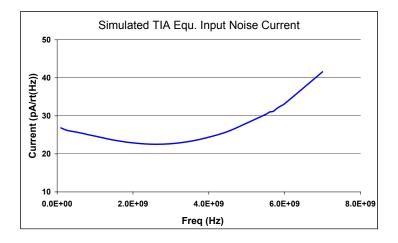

| 3.24 | Simulated input-referred noise current of the TIA in AMS C35 1                                                                                                                                                                          | 16 |

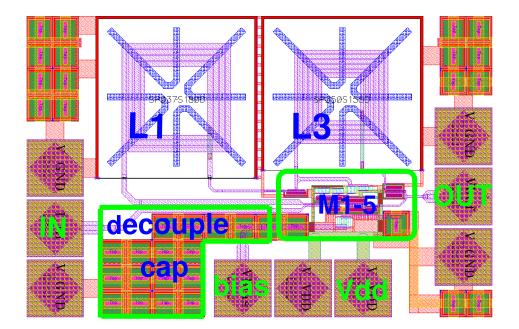

| 3.25 | Layout of the TIA in AMS C35                                                                                                                                                                                                            | 17 |

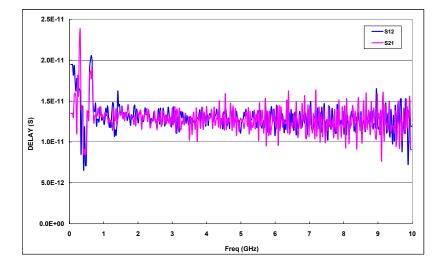

| 3.26 | The verification delay time after calibration from 40 MHz to 10<br>GHz (standard 14 ps)                                                                                                                                                 | 19 |

| 3.27 | TIA frequency measurement set up                                                                                                                                                                                                        | 20 |

| 3.28 | TIA die micrograph                                                                                                                                                                                                                      | 20 |

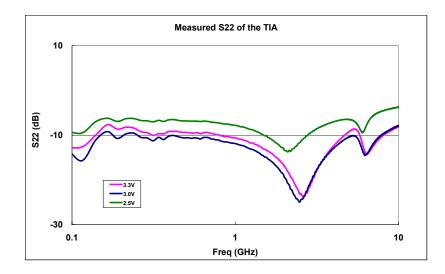

| 3.29 | Measured S22 of the TIA under different power supply 1                                                                                                                                                                                  | 21 |

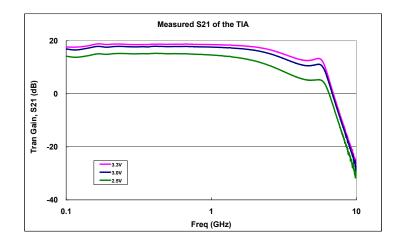

| 3.30 | Measured S21 of the TIA under different power supply 1                                                                                                                                                                                  | 22 |

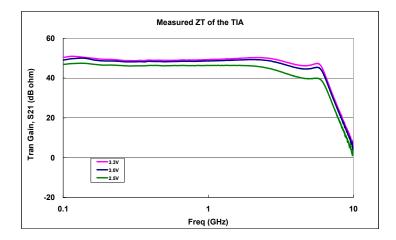

| 3.31 | Measured transimpedance gain (ZT) of the TIA under different power supply                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

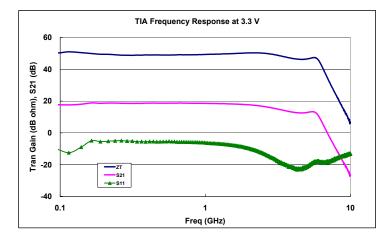

| 3.32 | Measured transimpedance gain (ZT), S21 and S22 of the TIA at power supply of 3.3 V                                                                     |

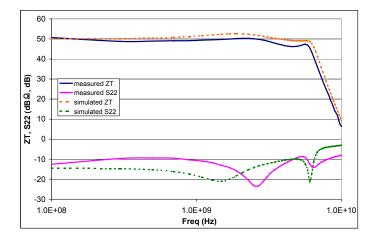

| 3.33 | Comparison between the measured and simulated results of the TIA at 3.3 V power supply                                                                 |

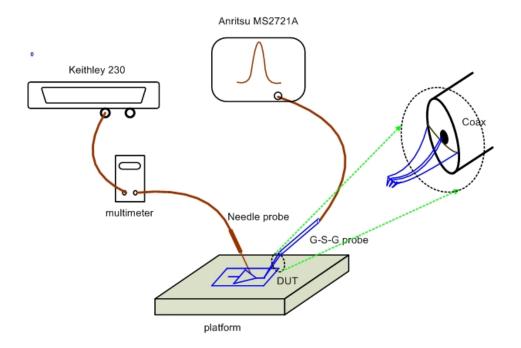

| 3.34 | TIA noise measurement set up                                                                                                                           |

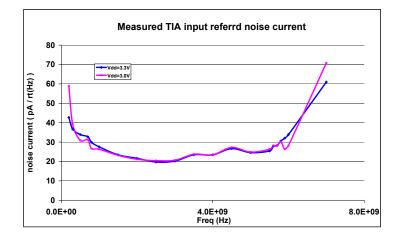

| 3.35 | Measured TIA input referred noise current at 3.3 V and 3.0 V power supply                                                                              |

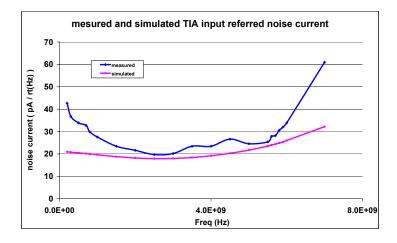

| 3.36 | Measured and simulated TIA input referred noise current 127                                                                                            |

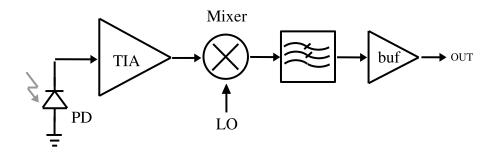

| 4.1  | Block diagram of the optical front-end                                                                                                                 |

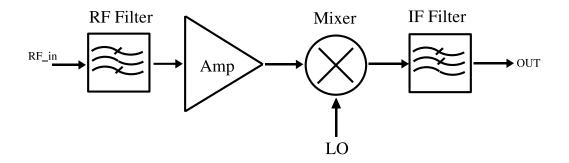

| 4.2  | A typical RF receiver architecture                                                                                                                     |

| 4.3  | Single-Balanced Active mixer                                                                                                                           |

| 4.4  | Double-Balanced Active mixer                                                                                                                           |

| 4.5  | Single -Transistor Active mixer                                                                                                                        |

| 4.6  | Dual-Gate FET mixer                                                                                                                                    |

| 4.7  | Noise aliasing from harmonic LO sidebands                                                                                                              |

| 4.8  | 3-order intercept- and compression points                                                                                                              |

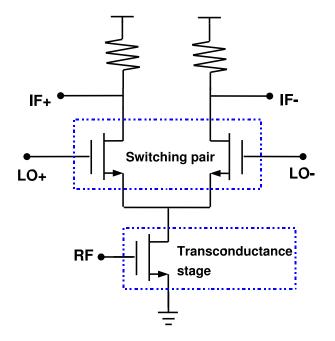

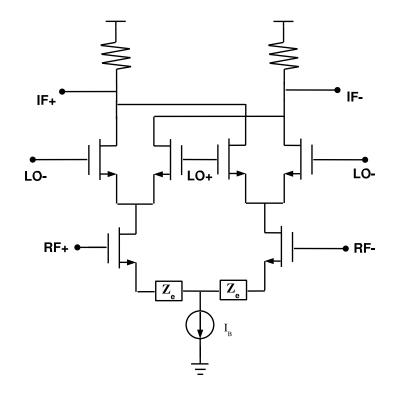

| 4.9  | (a) Small signal analysis for differential pair (b) Gilbert cell as multiplier                                                                         |

| 4.10 | (a) Gilbert cell in switching mode (b) mixer simplified circuit<br>with LO between RF and IF (c) mixer simplified circuit with RF<br>between LO and IF |

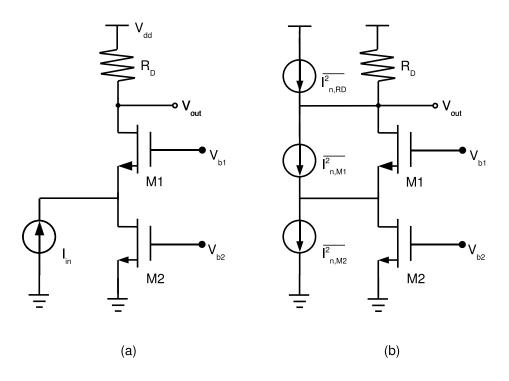

| 4.11 | (a) Cascode stage; (b) noise of $M_2$ modeled by a current source . 147                                                                                |

| 4.12 | $f_{max}$ of NMOS transistor $24 \times 5 \times 0.35 \ \mu m$ in AMS C35, $V_{ds}$ =1 V (+), 2 V ( $\circ$ ) and 3 V ( $\times$ )                     |

| 4.13 | Q factor of the inductor SP037S180D (3.7nH) in AMS C35 150                                                                                             |

| 4.14                                                                                           | Q factor of the poly-poly capacitor (1 pF) in AMS C35 150                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.15                                                                                           | Matching network for (a) $R_p$ larger than $R_s$ ; (b) $R_p$ smaller than $R_s$ . 151                                                                                                                                                                                                   |

| 4.16                                                                                           | The reflection coefficients at the RF port $(S_{11})$ , LO port $(S_{22})$ and D2S output port $(S_{33})$                                                                                                                                                                               |

| 4.17                                                                                           | Schematic of the LO driver                                                                                                                                                                                                                                                              |

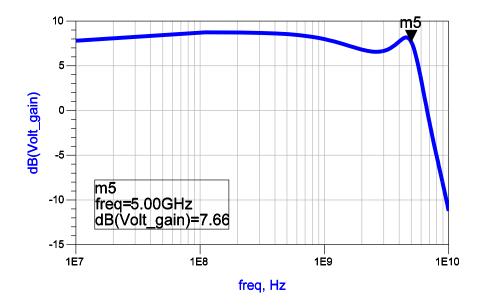

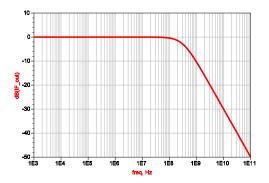

| 4.18                                                                                           | The frequency response of the LO driver                                                                                                                                                                                                                                                 |

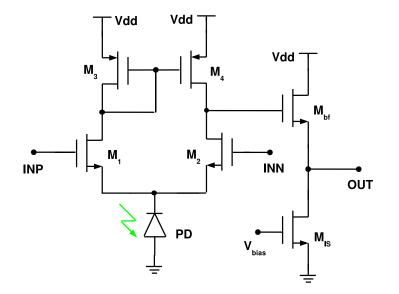

| 4.19                                                                                           | Schematic of the Differential to Single circuit                                                                                                                                                                                                                                         |

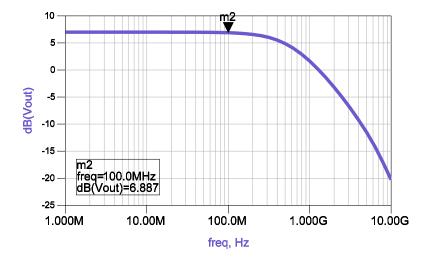

| 4.20                                                                                           | AC simulation result of the D2S                                                                                                                                                                                                                                                         |

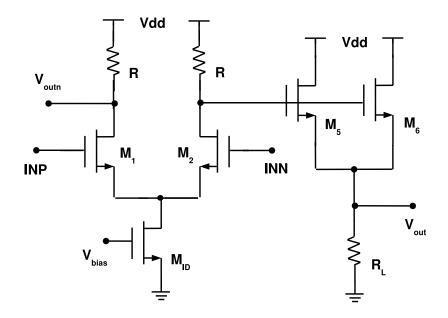

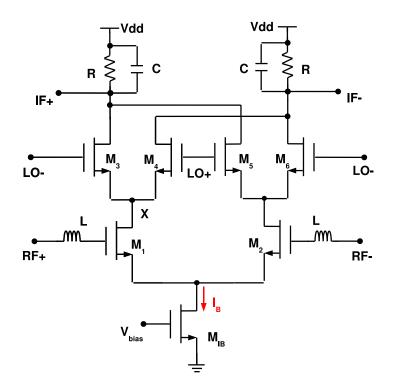

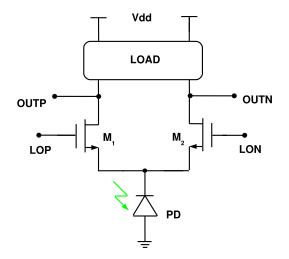

| 4.21                                                                                           | Schematic of the mixer core                                                                                                                                                                                                                                                             |

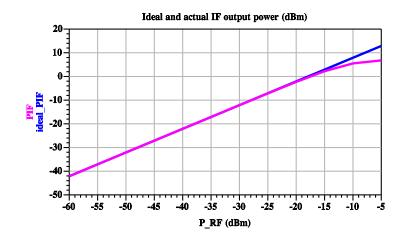

| 4.22                                                                                           | Mixer IF output vs RF input power at 5 GHz RF input and 100<br>MHz IF                                                                                                                                                                                                                   |

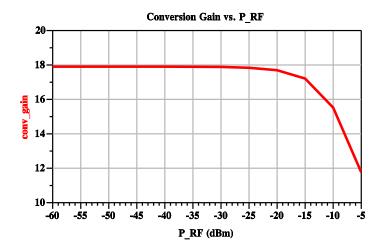

| 4.23                                                                                           | Mixer conversion gain vs RF input power at 5 GHz RF input and 100 MHz IF                                                                                                                                                                                                                |

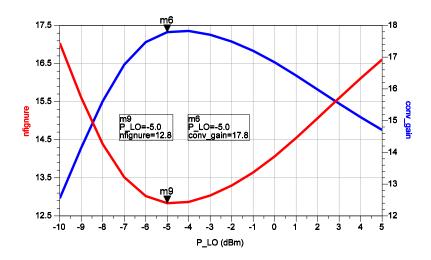

| 4.24                                                                                           | Simulated mixer noise figure and conversion gain vs LO power.                                                                                                                                                                                                                           |

|                                                                                                | RF=5 GHz, IF=100 MHz                                                                                                                                                                                                                                                                    |

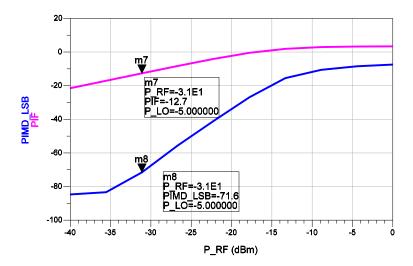

| 4.25                                                                                           |                                                                                                                                                                                                                                                                                         |

|                                                                                                | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vs                                                                                                                                     |

| 4.26                                                                                           | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vs165                                                                                                                                  |

| 4.26<br>4.27                                                                                   | RF=5 GHz, IF=100 MHz.       163         Simulation of Input IP3 of the mixer vs input RF power       164         Simulation result of input IP3 and conversion gain of the mixer vs       165         LO power       165         Layout of the mixer in RF1       166                   |

| 4.26<br>4.27                                                                                   | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vs165                                                                                                                                  |

| <ul><li>4.26</li><li>4.27</li><li>4.28</li></ul>                                               | RF=5 GHz, IF=100 MHz.       163         Simulation of Input IP3 of the mixer vs input RF power       164         Simulation result of input IP3 and conversion gain of the mixer vs       165         LO power       165         Layout of the mixer in RF1       166                   |

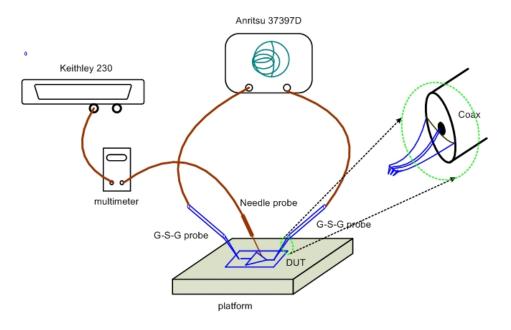

| <ul><li>4.26</li><li>4.27</li><li>4.28</li><li>4.29</li></ul>                                  | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vsLO power165Layout of the mixer in RF1166Mixer measurement setup167                                                                   |

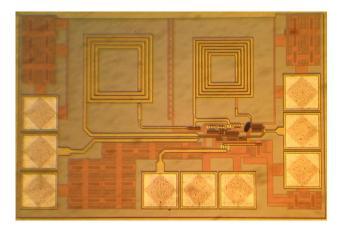

| <ul> <li>4.26</li> <li>4.27</li> <li>4.28</li> <li>4.29</li> <li>4.30</li> </ul>               | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vsLO power165Layout of the mixer in RF1166Mixer measurement setup167RF1 mixer die micro graph167                                       |

| <ul> <li>4.26</li> <li>4.27</li> <li>4.28</li> <li>4.29</li> <li>4.30</li> <li>4.31</li> </ul> | RF=5 GHz, IF=100 MHz.163Simulation of Input IP3 of the mixer vs input RF power164Simulation result of input IP3 and conversion gain of the mixer vsLO power165Layout of the mixer in RF1166Mixer measurement setup167RF1 mixer die micro graph167Measured mixer S11 at RF input port170 |

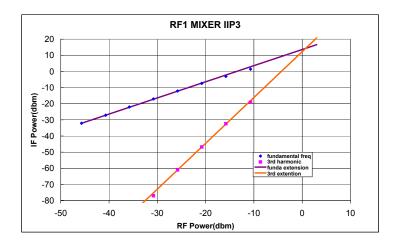

| 4.34 | Measured mixer's fundamental and 3rd harmonics output power                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------|

|      | at two-tone RF input at 4.8 GHz and 4.805 GHz while LO=4.9                                                                    |

|      | GHz. IIP3 can be extrapolated to be about 1.5 dBm 173                                                                         |

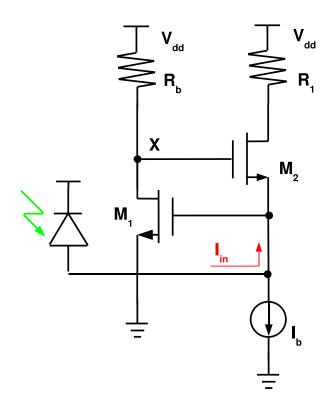

| 5.1  | Block diagram of the mixer based optical front-end                                                                            |

| 5.2  | Schematic of the mixed based optical front end                                                                                |

| 5.3  | Simulated bandwidth of the mixed based optical front end with a DC=100 <i>nA</i>                                              |

| 5.4  | Transient simulation on the mixed based optical front end with a $DC=100 nA$ and a modulation depth of 10%. LO= 5 MHz, IF=300 |

|      | KHz                                                                                                                           |

| 5.5  | Layout of the mixed based optical front end in AMS $0.35 \mu m$ CMOS186                                                       |

| 5.6  | Evaluation board of the mixed based optical front end                                                                         |

| 5.7  | Measured frequency response of the mixer based optical front end 188                                                          |

| 5.8  | Block diagram of the optical front-end                                                                                        |

| 5.9  | Schematic of the Differential to Single circuit in the 5 GHz optical front end                                                |

| 5.10 | Simulated frequency response of the 5GHz optical front end 191                                                                |

| 5.11 | Post layout transient simulation results of the 5 GHz optical front-end192                                                    |

| 5.12 | The layout of the 5GHz optical front end in AMS C35 193                                                                       |

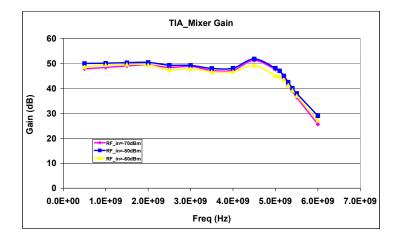

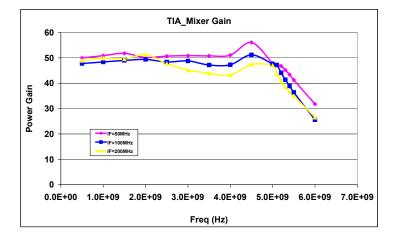

| 5.13 | The measured frequency response of the TIA based optical front<br>end with different RF input power                           |

| 5.14 | The measured frequency response of the TIA based optical front<br>end with IF frequency of 50 MHz, 100 MHz and 200 MHz 195    |

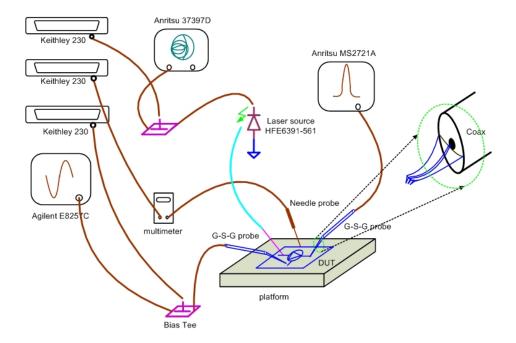

| 5.15 | The measurement setup of the TIA based optical front end 196                                                                  |

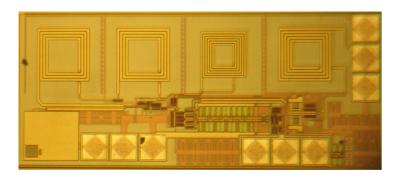

| 5.16 | The die micrograph of the TIA based optical front end 196                                                                     |

| 5.17 | The measured frequency response of the TIA based optical front                                                                |

|      | end                                                                                                                           |

### LIST OF FIGURES

| 5.18 The meas | sured input referred noise current of the TIA based optical |     |

|---------------|-------------------------------------------------------------|-----|

| front end     |                                                             | 198 |

# **List of Tables**

| 2.1 | Extracted PMOS drain-bulk parasitic capacitance $(fF)$                                   | 49    |

|-----|------------------------------------------------------------------------------------------|-------|

| 2.2 | Calculated strip numbers of photodiode based on the extracted $C_{jd}$                   | 50    |

| 2.3 | Comparison of the two fabricated photodiodes                                             | 50    |

| 2.4 | Main performance parameters of HFE4080-32X-XBA                                           | 54    |

| 2.5 | Main performance parameters of HFE6391-561                                               | 56    |

| 2.6 | Dark current of the photodiodes with different reverse biased voltage applied            | 58    |

| 2.7 | The measured performances of the photodiodes                                             | 66    |

| 3.1 | Shunt-peaking summary                                                                    | 98    |

| 3.2 | Normalized 3-dB bandwidth with different inductance <i>L</i> for amplifier in Fig. 3.14. |       |

| 3.3 | Optimized component values of the TIA                                                    | 111   |

| 3.4 | The calibration coefficients for $100\mu m$ G-S-G probe from Cascade Microtech           | 118   |

| 3.5 | The noise level of MS2721A at different frequencies with RBW=10                          |       |

|     | Hz                                                                                       | 126   |

| 3.6 | Comparison of recently published high speed TIA in CMOS technolo                         | gy128 |

| 4.1 | Design values of the LO driver                                                           | 155   |

| 4.2 | Design values of the LO driver                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.3 | Design values of the mixer core                                                                                                                                |

| 5.1 | Comparison of published fully integrated optical receivers. ( * refers to analog bandwidth instead of data rate. **Ge-SOI PD bonded on 0.13- $\mu$ m CMOS) 178 |

| 5.2 | Design values for the devices in the mixer based optical front end . 186                                                                                       |

| 5.3 | The performance summary of the optical front end                                                                                                               |

# Chapter 1

# Introduction

The work presented in this thesis is concerned with the realization of a high speed optical front end in CMOS process which senses and demodulates the light signal in an optical sensing system. The system finds applications in solid material non-destructive testing, i. e., flaw detection and material characterization by acquiring images of the interaction between surface acoustic waves (SAWs) and a solid material. It uses lasers to generate and detect the SAWs, and has been developed as an accurate non-contacting laser based system for high resolution surface waves measuring and imaging. The generated surface acoustic waves will be reflected and changed when they propagates along the surface of the solid material, which can be imaged by an optical sensor. Basically, the surface acoustic waves contain a fundamental frequency which is determined by the laser generation system, but they are also rich in high frequency harmonics, which can be up to tens GHz. For the purpose of improving the spatial resolution of the imaging and thus the better accuracy of the non-destructive testing, a high speed back end optical sensor plays an important role in the system for flaw detection or material characterization.

Much of this work is focused on the design, analysis and implementation of the devices and circuits for the high speed optical front end in a low cost CMOS  $0.35\mu m$  process. Prior to the main part of the thesis, chapter 1 gives a brief description about the applications of non-destructive testing which addresses the principles of photoacoustic waves and laser generation and detection systems.

### **1.1 Photoacoustic History**

The photoacoustic effect was discovered by Alexander Graham Bell in 1880 [1, 2], when he observed how focusing a "rapidly-interrupted" beam of sunlight onto a thin diaphragm of material resulted in a "clear, musical tone[2]." Postulating the "sonorousness" under these conditions was a fundamental property of matter, Bell devised a method for studying the effect in solids, liquids and gases. He tested a variety of substances including potash, selenium, tobacco smoke, cork, platinum, ink, wool, and even a cigar. Bell, who had just made his famous telephone call to Watson in the spring of 1876, hoped to use the photoacoustic effect to create a "photophone", a device like the telephone, but with the signal transmitted as light rather than electricity. Perhaps Bell anticipated the advantages of optical networks. These discoveries were then further investigated and published in 1881 [3].

Similar experiments on gases were performed by John Tyndall and Wilhelm Rntgen in 1881 after hearing about Bell's discovery. Then the field lay dormant for 50 years until the discovery of the microphone made it possible to enhance the measurements. In 1938 Viengrov at the State Optical Institute of Leningrad used the method to study infrared absorption in gases and the gas content in gas mixtures. Pfund developed a gas analyser in 1939 which was used in John Hopkins Hospital in Baltimore to measure CO and  $CO_2$ . Luft developed a commercial gas analyser which became available in 1946. The interest in photoacoustic grew in this period and it was only used to monitor gases. When the infrared spectrometer was invented, a more accurate method for monitoring gases existed so the field again lay dormant until 1970[4, 5].

It was the invention of the laser that gave the field of photo acoustics new possibilities. Consequently, the photoacoustic effect remained largely a scientific curiosity until Kreuzer combined photoacoustic detection with lasers to demonstrate extremely sensitive gas detection in 1971 [3]. Kreuzer then went on to demonstrate photoacoustic detection for pollution monitoring [4, 5], and for gas chromatograph detection [6]. Dewey et al. [7] improved the sensitivity of photoacoustic detection systems further by modulating the optical excitation at a frequency corresponding to an acoustic mode in the cavity. In the late seventies, the field of photoacoustic exploded, finding commercial applicability today in trace gas analysis, pollution monitoring, biological studies and material characterization [8], which section 1.3 goes to detail.

Figure 1.1: Bell's plan for photophone[2]

### **1.2** Physics Behind Photoacoustic

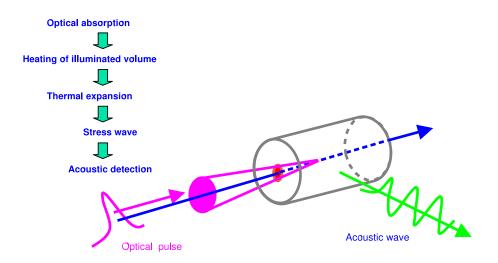

Much theory has been developed to explain the phenomenon of photoacoustics [8]. This section presents the fundamental elements in understanding the physics behind photoacoustics. Generally high energy light is used, usually a laser, firing into the test sample. When the laser hits the sample, some of the energy is absorbed by the molecules in the media resulting in a region of higher temperature. The rise in temperature will generate an expanding region and a pressure wave will propagate away from the source. This decaying pressure wave can be then picked up by a transducer or a laser imaging system. The phenomenon is due to the fact that the molecules in the sample being monitored have a quicker response to light than to the surrounding media. The process is shown in Fig. 1.2.

The thermal elastic expansion mechanism is an interesting choice for material characterization and medical diagnosis for a variety of reasons. Firstly, it does not break or change the properties of the object under study. Secondly, it has a linear or a definite relationship with many of the physical parameters of diverse materials. Thirdly, it is non-destructive or non-invasive in applications such as materials test and medical diagnosis.

Figure 1.2: Photoacoustic generation

### **1.3** Non-Destructive Test (NDT)

NDT involves testing an object for its integrity and fitness without damaging the object. There are many different general methods of testing objects nondestructively. These methods include optical inspection, radiographic testing, magnetic particle inspection, holographic testing, acoustic emission and, of course, ultrasonics testing [9]. The role of ultrasonics in NDT can be split broadly into two areas; that of flaw detection, and material characterization. There is also a slight crossover in the area of flaw characterization. The interaction of ultrasonic waves with the material and features therein can be used to ascertain the presence of flaws (and perhaps their nature) or some physical or chemical characteristic of the material under test.

#### **1.3.1** Flaw Detection

A common requirement for a NDT process is to determine whether any flaws are present that will adversely affect the operation or lifespan of a component. Typical flaws include surface-breaking or interior cracks, weak joints, coating delamination or loss of adhesion between coating and substrate. There are several methods of detecting flaws with acoustic waves, and obviously different methods are appropriate for different types of flaws, the use of a particular technique depends on many factors, including sample geometry, attenuation, and the characteristics of any possible flaws. In a named pulse-echo techniques, the existence of a flaw is determined by the reflection of ultrasound, which is detected by the combined transmitter/receiver, the location of the flaw from the transmitter can be calculated by the "time of flight" of the received ultrasound if the velocity of the acoustic waves in the material under investigation is known.

In general, the higher the acoustic waves frequency, the higher the resolution, both spatial and temporal, but with the disadvantage that losses caused by scattering and aberration are higher [9].

#### **1.3.2** Material Characterization

The characterization of materials is another important area of NDT. Characterization can include ascertaining various dimensions (for example the thickness of the steel), coating thickness, porosity, residual stress, grain size in the case of multi-grained materials such as metals, or grain orientation in single-grained materials such as silicon. The characterization may be required mid-process, in which case the ultrasonic inspection may provide a means of process control, or post-process, in which case it provides a means of quality management [9].

In terms of geometry characterization, the pulse-echo method, is the most common form of ultrasonic inspection, whereby the time taken for an ultrasonic pulse to be reflected off the rear surface of the material is related to the thickness of the material. Knowledge of the wave velocity is necessary, but for many materials this has been well known for many years.

The velocity of ultrasonic waves is the primary means of many forms of characterization, since it is a function of the moduli of elasticity and density. Changes in velocity can therefore correlate with changes in the material properties such as porosity, residual stress or, in the case of surface waves, coating thickness. If the change in property is the result of a process that the material is being subjected to, then examination of the velocity may provide a means of monitoring the process concerned.

### **1.4 O-SAM in University of Nottingham**

An all-Optical Scanning Acoustic Microscope System (O-SAM), which involves a totally non-contact method of acquiring images of the interaction between surface acoustic waves (SAWs) and a solid material has been set up by applied optics group in the University of Nottingham [12]. The system uses lasers to generate and detect the SAWs, and has been developed from an accurate non-contacting laser based system for surface wave velocity measurement [13].

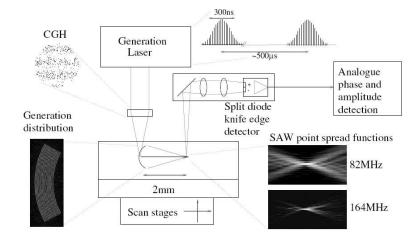

Fig. 1.3 shows the key parts of the O-SAM system. Two lasers are involved, one for ultrasound generation, the other for detection of the ultrasound. Both are associated with some optics and mechanical stages (for adjustment and scanning) and some electronics and data acquisition equipment.

The energy from the pulsed generation laser is applied to the surface of the sample via optics that both focus the light onto the sample and control its spatial distribution (CGH means Computer Generated Hologram). This control of the generation profile is necessary to obtain the large surface acoustic wave amplitudes required. The sample is mounted on automated mechanical stages to enable the formation of scanned images. The excited surface acoustic waves propagate on the sample surface, and are then detected by focusing a continuous wave laser onto the sample surface and measuring the angular deflection. Analogue amplitude and phase detection electronics then amplify and convert the signals from the detectors into a form suitable for acquisition by a host computer.

Figure 1.3: Diagram of all-Optical Scanning Acoustic Microscopy (O-SAM) [12]

The acoustic frequencies are determined by the generation laser. This is a Q-switched, mode locked laser, producing a tone-burst of approximately 30 very short pulses (200 *ps*) separated by 12.1 *ns* with a variable repetition rate (up to 5 KHz). The average power output of the laser is around 2 *W* (depending on the repetition rate); at low repetition rates (below 2 KHz) the peak power reaches a maximum, whereas above this it decreases with increasing repetition frequency. The signal has a fundamental frequency of 82 MHz (which is determined by the laser generation source) and contains harmonics of this. Higher frequencies have been observed up to 10 GHz [12]. This thesis is working on the implementation of high speed optical front end to allow greater spatial resolution of the acoustic wave imaging system.

# **Chapter 2**

# **Photodetector**

### 2.1 Introduction

Photodetectors are the components in an optical receiver system that convert optical energy into electrical energy. They are involved in applications of imaging, communications, and optical sensing. CCD (Charge Coupled Device) and CMOS sensors represent the widely used photodetectors for imaging system, and the competition between the two technologies continues today. Low noise, low power, low cost, and high sensitivity are always of great concern for these systems.

Different from imaging systems, the speed of the photodetectors in optical communication and sensing systems is generally the first priority instead. High speed, high sensitivity photodetectors are generally made from III-V compound to achieve the highest possible performance for long haul optical communications. However, the high cost of these materials limits their use in optical sensing systems, as in this thesis. Short wavelength light sources (shorter than 850*nm*) and a high speed, inexpensive photodetector which can be integrated in low cost photo receivers is the design target for this work.

### 2.2 **Principles of Photodetection**

A photodetector converts light energy into electrical energy, manifested usually in the form of photocurrent[23]. Semiconductor photodetectors rely on the absorption of incident photons with energy greater than the semiconductor bandgap energy to generate electron-hole pairs (EHPs). Photodetection broadly involves three processes [24]:

- Absorption of optical energy and generation of carriers;

- Transportation of photogenerated carriers away from the absorption region;

- Carrier collection and generation of photocurrent.

The performance of a photodetector can be characterized by various figures of merit. These include the responsivity of the detector, its bandwidth, and the noise added to the signal by the detector.

**Responsivity** Responsivity is a measure of light-to-current conversion efficiency of the detector. A high detector responsivity improves the signal-to-noise ratio of the receiver system. It is possible to have gain in photodetectors (as in avalanche photodetectors) due to impact ionization and avalanche multiplication that can lead to very high responsivities. But these mechanisms are usually accompanied by a penalty in bandwidth and noise performance. Mathematically, the responsivity of a detector, R, is defined as [36]

$$R = \frac{I_{ph}}{P_{inc}}$$

where  $I_{ph}$  is the photocurrent,  $P_{inc}$  is the incident optical power.  $\eta$  is sometimes defined as the external quantum efficiency representing the fraction of incident photons leading to  $I_{ph}$ . In reverse biased junction photodiodes where the depletion region (high field region) constitutes the bulk of the absorption region, it can be approximated by

$$\eta = \eta_i (1-R) \left(1 - \frac{e^{-\alpha d}}{1 + \alpha L_n}\right) \tag{2.1}$$

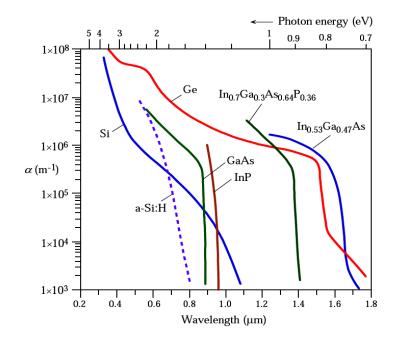

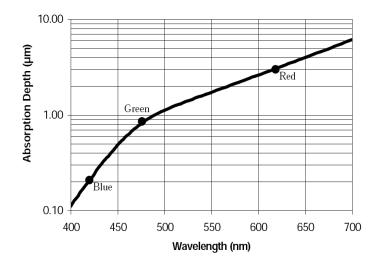

where *R* is the optical reflectivity between air and the semiconductor,  $\alpha$  is the absorption coefficient of the intrinsic region, *d* is the depletion region thickness and  $\eta_i$  is the internal quantum efficiency defined as the ratio of number of EHPs created to the number of absorbed photons. In pure material,  $\eta_i$  is almost unity.  $L_n$  is the minority carrier diffusion length, *i.e.* for electrons in the p-type substrate. In the absence of diffusive transport, the term  $\alpha L_n$  is missing in (2.1), and  $(1 - e^{-\alpha d})$  represents the fraction of light absorbed in the depletion width of the detecting junction. Note  $L_n = \sqrt{D_n \tau_n}$ , where  $D_n$  is the diffusion constant and  $\tau_n$  is the minority carrier lifetime [46]. Fig. 2.1 shows the optical absorption coefficient for general semiconductor materials.

Figure 2.1: Optical absorption coefficients for various materials[45, 46]

**Bandwidth** The bandwidth of a photodetector is defined as the frequency at which the responsivity of the detector has fallen by 3-dB from its low frequency

#### CHAPTER 2. PHOTODETECTOR

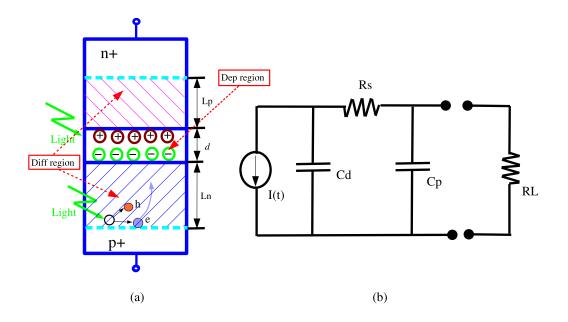

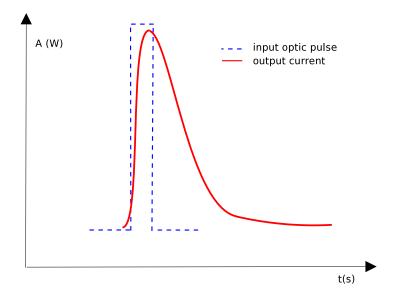

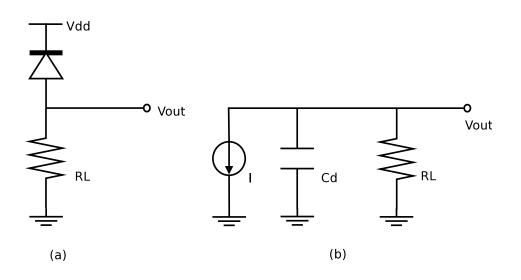

value. It is limited mainly by carrier transit time, RC time constant, diffusion time by photogenerated carriers outside the depletion region [38]. Carrier transit time is the time taken by photogenerated carriers to travel across the high-field region. It is usually dominated by hole transit time, as holes typically have a lower drift velocity than electrons in common photodetector materials. The RC time constant is determined by the equivalent circuit parameters of the photodiode and the load circuit. Diode series resistance (due to ohmic contacts and bulk resistances), load impedance, and the junction and parasitic capacitances contribute to the RC time constant. Diffusion time becomes important when the photocurrent due to carriers absorbed in the p and n contact regions within about one diffusion length of the edge of the depletion region becomes comparable to the current arising from photogenerated carriers within the depletion region. In Fig. 2.2 (a), the depletion and diffusion regions of a typical p-n junction photodiode are illustrated where d stands for depletion region width,  $L_n$ ,  $L_p$  for diffusion length of electrons and holes in the semiconductor (practically,  $L_n$ ,  $L_p$  are much longer than d, which is not as shown as in Fig. 2.2). The transit time then can be written as d/v (v is the saturation velocity of holes); diffusion time is determined by the time that the electrons take to get through the lower diffusion region in Fig. 2.2 (a) or the holes via the upper one. Because the diffusion process is driven by the random motion of carriers, it is a slow transport mechanism. This was interpreted and experimentally confirmed in the work of [39, 40]. In this case, the diffusion component contributes a slow but long tail to the detector's impulse response which significantly limits its high frequency response. Detailed analysis is given in following sections.

A simple equivalent circuit of a *p*-*n* photodiode is given in Fig. 2.2 (b). If the parasitic capacitance  $C_p$  and series resistance  $R_s$  are negligible, then the *RC*-limited bandwidth can be given by

$$f_{RC} = \frac{1}{2\pi R_L C_d} \tag{2.2}$$

$$C_d \propto \frac{A}{X_d} \tag{2.3}$$

$$X_d = \sqrt{\frac{2\varepsilon_0\varepsilon_i}{q}}\left(\frac{1}{N_n} + \frac{1}{N_p}\right) \cdot \left(\triangle V + \phi_i\right) \tag{2.4}$$

$$\phi_i = \frac{kT}{q} lg\left(\frac{N_n \cdot N_p}{N_i^2}\right) \tag{2.5}$$

where  $R_L$  is the load resistance,  $C_d$  is the photodiode junction capacitance, A is the area of the diode,  $X_d$  is the depletion width of the junction,  $N_p$  and  $N_n$  are impurity concentration of p, n region,  $\Delta V$  is the reverse biased voltage applied to the photodiode, and  $\phi_i$  is the junction potential across the p-n junction.  $\varepsilon_0$ is the dielectric constant in vacuum,  $\varepsilon_i$  is the relative dielectric constant of the semiconductor, k is the Boltzmann constant, T is the absolute temperature in K, q is the electronic charge,  $N_i \approx 1.3 \times 10^{10} cm^{-3}$  is the intrinsic carrier density of silicon at T. It can be seen from equations (2.3), (2.4), shrinking the size of the diode, increasing the reverse bias voltage and lowering doping level lead to smaller  $C_d$ . But the smaller diode area generally means smaller window to the light incident and degrades the responsivity; reverse bias voltage is limited by breaking down voltage; changing doping level is not always available for integrated photodetectors such as in CMOS. Hence there are lot of trade offs in bandwidth optimization of the photodiodes.

Figure 2.2: (a) PN junction as a photodiode (b) equivalent circuit for a p-n junction photodiode

For discrete photodetectors,  $R_L$  is usually assumed to be 50  $\Omega$  because most of the RF test instruments used for device characterization are designed to have an input impedance of 50  $\Omega$ . In photo receivers, the input impedance of the amplifier following the photodetector is often designed to be lower than 50  $\Omega$  to improve the circuit bandwidth.

**Noise** The photodetector not only produces the signal current  $I_s$ , but also noise. Shot noise and thermal noise are two dominant sources of noise in high-speed photodetectors. Shot noise current is the result of the photocurrent being composed of a large number of short pulses that are distributed randomly in time. Each pulse corresponds to an electron-hole pair created by a photon. With white noise approximation, its mean-square value turns out to be [41]

$$\overline{i_n^2} = 2qI \cdot BW_n \tag{2.6}$$

where q is the electron charge, I is the signal current and  $BW_n$  is the bandwidth in which we measure the noise current<sup>1</sup>. The photodetector produces a small amount of current even when it is in total darkness. This so called *dark current*, depends on the junction area, temperature, and processing. It manifests itself as shot noise, contributes to the total system noise and gives random fluctuations about the average particle flow of the photocurrent [41]. Since most photodiodes are operated under reverse bias conditions, the dark current is usually quite small when compared to the that of the following transimpedance amplifier in operating condition<sup>2</sup>.

Thermal noise in photodetector is caused by the various resistances in diode's equivalent circuit. Diode shunt resistance and series resistance both contribute to the thermal noise. If the diode is followed by an amplifier in a receiver circuit, then the input resistance of the amplifier and the amplifier's noise also contribute to the thermal noise of the overall photo receiver.

Apart from these noise sources, there is also a contribution from the background radiation in the ambient where the detector is placed. Usually, the contribution of the amplifier dominates noise performance in a photo receiver at telecommunication wavelengths. Detailed noise analysis of the optic front end is presented in chapter 3, the transimpedance amplifier design.

### 2.3 Overview of High Speed Photodetectors

There are many different types of high speed photodetectors possible with the most appropriate kind of detector being determined by the different application. With architecture concerned, *p-i-n*, Metal-Semiconductor-Metal (MSM), and Avalanche Photodiodes [44, 23] are generally referred to and are discussed below.

<sup>&</sup>lt;sup>1</sup>It is noted that avalanche photodiode has a much bigger noise current than that calculated from (2.6) because of the excess noise factor introduced by randomness of avalanche multiplication process [41].

<sup>&</sup>lt;sup>2</sup>This would be another case in the application of CMOS photodetector as APS (Active Pixel Sensor) at low frequency range.

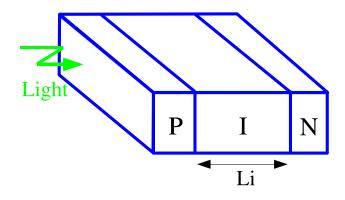

#### 2.3.1 *p-i-n* Photodiode

A *p-i-n* photodiode consists of a *p-n* junction with a layer of intrinsic or lightly doped semiconductor sandwiched between the *p* and *n* layers. The intrinsic region has a small number of carriers and is easily depleted of any charge. Therefore, the depletion region is almost entirely contained in the intrinsic region. Fig. 2.3 shows a *p-i-n* photodiode together with its electric field [25]. Light absorbed in the semiconductor produces electron-hole pairs, however, due to the substantial electric field in the depletion (intrinsic) region, pairs produced in the depletion region or within a diffusion length of it, will be separated by the electric field leading to current flow in the external circuit.

Figure 2.3: *p-i-n* photodiode

Very high speed and high sensitivity compound semiconductor p-i-n photodiodes have been reported in literature. For example, a waveguide integrated *p-i-n* photodiode (WG PIN PD) with a 3 dB bandwidth of > 40 GHz at 1550 *nm* was demonstrated by Wang *et al* [26]. In [27], 1550 *nm* InP/GaInAs/InP *p-i-n* photodiodes have been fabricated with speeds of up to 60 GHz. However, despite the high bandwidth and high sensitivity clearly achievable with compound semiconductors, there is an eagerness to produce silicon long wavelength photodetectors. This is, again, due to the low cost, large scale integration achievable with silicon. A possible means of extending the spectral response of silicon into the long wavelength region has been to use heterostructures composed of silicon (Si) and germanium (Ge). Many successful reports of *p-i-n* SiGe/Si superlattice photodetectors have been made for wavelengths of 850-1300 *nm*. For instance, Temkin *et al* developed a 1300 *nm* GeSi/Si waveguide *p-i-n* photodiode that operated at speed > 1 GHz and had an internal quantum efficiency of 40% [29], while Tashiro et al demonstrated a 10.5 GHz, 980 *nm* planar *p-i-n* SiGe/Si diode with an external quantum efficiency of 25-29% [30].

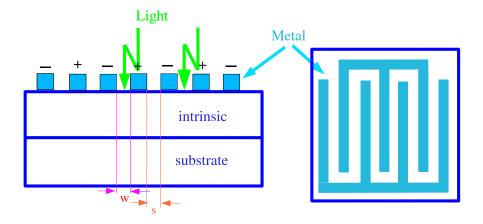

#### 2.3.2 MSM Photodiode

a MSM PD is comprised of back-to-back Schottky diodes that use an interdigitated electrode configuration on an undopped semiconductor layer, as shown in Fig. 2.4. When light with energy  $hv > E_g$  is incident, the light that hits the semiconductor surface is absorbed and creates electron-hole pairs (EHs) within the active region, and then one set of electrodes acts as a cathode and the other as an anode. The holes drift toward the negative electrodes, and electrons travel to the positive electrodes under the influence of an electric field by an applied reverse bias voltage [32, 33].

The metal electrode fingers have finger width w and are separated by a distance s. High photodiode quantum efficiency requires  $s \gg w$ , or low electrode shadowing as it is termed. Absorbed photons generate electron-hole pairs in the semiconductor, the holes drift with the applied electric field to the negative contacts while the electrons drift to the positive contacts forming a current ( $i_{photo}$ ). The bandwidth of a MSM diode is similar to that of a *p-i-n* detector in that it is both RC time constant and transit time limited.

Figure 2.4: MSM photodiode cross section and top view

MSM photodiodes have simple, planar structures and can easily be fabricated with FET (field effect transistor) processes provided that the substrate is highly resistive or intrinsic epitaxy layer is available. They have also been shown to operate to very high speeds with bandwidths of 510 GHz on low temperature (LT) GaAs and 110 GHz on bulk silicon reported [34, 35]. The silicon photodiode, however, achieved this speed at very short wavelengths (400 *nm*) and at longer infrared wavelengths (800 *nm*) this speed became diffusion limited.

Although superior for its least complexity and high speed performance, MSM photodiodes are always associated with problems of quite low responsivity because of the reflection from the surface metals and semiconductor surface; the finite carrier lifetime as the carriers traverse the gap between the electrodes before being collected; absorption of incident light outside the region in which photogenerated carriers can be collected by the electrodes; and surface recombination currents and deep traps within the semiconductor material which may lower the detected optical signal. Furthermore, similar to p-i-n photodiode, it is not compatible with CMOS process.

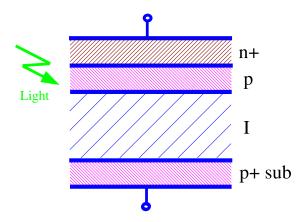

#### 2.3.3 Avalanche Photodiode

Avalanche photodiodes differ from p-i-n and MSM diodes in that they incorporate a high field region that multiplies the photocurrent through the avalanche generation

of additional electron-hole pairs. The operation of PIN diodes is based on the generation of one electron-hole pair for each photon entering the lattice. avalanche photodiodes (APDs), on the other hand, the generated electrons and holes carry so much energy that they themselves can stimulate other electrons and holes, creating an avalanche effect.

APDs operate with controlled avalanche, that is, with a multiplication factor, M, of several hundred. Thus, each photon entering the device may create hundreds of of electron-hole pairs, providing a large output current. Shown in Fig. 2.5 is the structure of a typical APD, consisting of a sandwich of n+, p, and i layers atop a p+ substrate. As in PIN diodes, the intrinsic region enables generation of electron-hole pairs. Grown as a very uniform and thin layer, the p region supports a high electric field to create avalanche.

Besides the internal gain and high responsivity, APDs suffer from "gain-bandwidth" trade off. That is, the higher the multiplication factor is, the longer the avalanche persists, limiting the changes of the current and the response to high frequency signal. Secondly, the reverse bias voltage applied to APDs must be controlled precisely so as to achieve avalanche while avoiding break down. Furthermore, it is incorporated with significant noise because of the noisy avalanche process [25].

Figure 2.5: Avalanche Photodiode

# 2.4 Overview of CMOS Photodetector

Since the invention of the integrated circuit, the electronics industry has been relentless in its quest to integrate the functions of the electronic systems onto single silicon chip. This process has generally resulted in both increased utility and decreased system costs, an outcome that tends to accelerate the trend [42]. CMOS technology has achieved the greatest success in this regard [43]. Aggressive scaling resulting from competition to follow Moore's law has improved the integration density of CMOS transistors by more than 3 orders of magnitude in the last 30 years, moreover, advanced CMOS devices can now achieve cutoff frequencies comparable to that of III-V compound devices.

A CMOS monolithically integrated photo receiver is therefore desirable for use in short distance connection systems and optical sensing systems based on its low cost, low power consumption, high reliability and potential for large scale integration. Here monolithic integration is necessary because integrated photodiodes can be beneficial since the capacitance at the input node of the preamplifier circuit is greatly reduced due to the elimination of bonding wire parasitics.

It is not yet possible, however, to realize a high speed, high sensitivity photodetector in a production CMOS process without adding complexity to the process. Presently, no commercial silicon photo receiver uses an integral, monolithic detector, instead an external detector is hybridized to the receiver resulting in increased cost, and decreased bandwidth due to interconnection parasitics [44].

To address the challenge for implementing integrated photodetectors in silicon, first we rewrite the equation (2.1) here:

$$\eta = \eta_i (1 - R) (1 - \frac{e^{-\alpha d}}{1 + \alpha L_n})$$

(2.7)

Two characteristic lengths associated with the problem are  $L_n$  and  $\alpha^{-1}$ . For *d* on the order of  $\alpha^{-1}$ , most of the carriers are collected rapidly by the depletion field, and diffusive transport can be made small. At moderate voltages, transport at saturation velocity is typical, and the cutoff frequency associated with such

transport is proportional to  $v_{sat}/d$ , which easily scales to very high speeds. On the other hand, in reasonably undamaged silicon the minority carrier lifetime can be in the milliseconds range, and diffusion lengths of 100*nm* or more are common. The cutoff frequency will scale as  $\tau_n^{-1} = D_n/L_n^2$ , and may be even in the kilohertz range. In a detector with a thin depletion region, diffusive transport will be a major fraction of the total current, making the device unsuitable for high-speed application.

Figure 2.6: Silicon absorption length[44]

Fig. 2.6 shows the silicon absorption length against the light wavelength. With wavelength of 800*nm*, the silicon absorption length is about  $15\mu m$ , while the depth of N-Well in a typical  $0.35\mu m$  CMOS is only  $1.8\mu m$ . From Fig. 2.1, it is clear that as an indirect gap material, silicon has a smaller optical absorption coefficient (thus longer absorption length) than the III-V compounds at the light wavelength above 800*nm*. This has a great impact on silicon photodetector's high frequency performance since lights with long wavelength penetrate deeper into silicon, thus causing unwanted diffusion current generated in the substrate. Consequently, it takes a long time for these carriers to reach the contact junctions. When light pulse impinges on the photodetector, the junction is intended to collect the early arriving *drift* carriers, as well as the delayed *diffusion* carriers. Sometimes, the delayed carriers are associated with previously received light pulses. This produces a slow

frequency gain effect that limits the cutoff frequency, while in time domain the impulse response has a long tail effect as shown in Fig. 2.7. Slow response times due to deferred carriers in the substrate are the major obstacle to high-speed fully integrated silicon-based receivers.

Figure 2.7: Diffusion long tail

However, despite the difficulties mentioned, continuously emerging techniques and solutions have been proposed [42, 52, 65, 61, 58, 67, 49, 50, 51], for integrating high speed photodetector in CMOS:

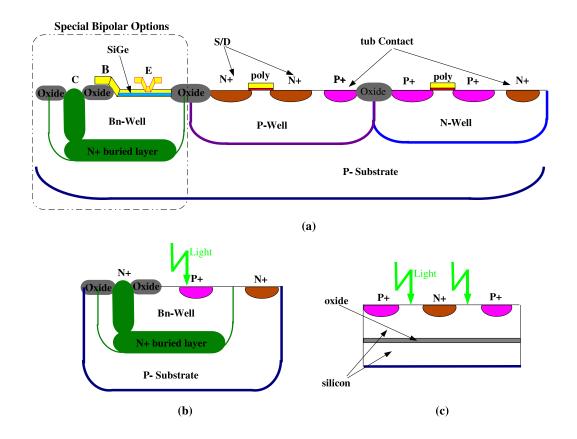

#### • 1. Screen the slow bulk carriers by buried layer or oxide layer

Workers at IBM first proposed this technique in detail for a fully integrated receiver in an unmodified BiCMOS process [47, 48]. This report explicitly describes the role of the buried collector contact as a screening terminal to remove the slow photogenerated bulk carriers, as shown in Fig. 2.8 (a), (b). The amplifier was entirely CMOS-based. The active detector was formed between the n-well of the BiCMOS process and p regions in the n-well. The buried collector layer, which makes contact to the n-well, forms a parasitic junction to the substrate, to which most of the slowly diffusing carriers are collected and screened from the amplifier,

so that a high speed of response is obtained. Although the shallow nature of the 0.5  $\mu m$  BiCMOS employed results in a low responsivity, their 75  $\mu m \times 75 \mu m$  detector achieved a 3-dB bandwidth of 700 MHz at 850 nm, Performance could be improved by moving to shorter wavelengths as noted by authors. The stated goal of the work was not the highest possible speeds, but the most affordable overall data-link costs, which gave rise to their use of a large photodiode area and short wavelength operation.

Figure 2.8: (a) simplified cross section of SiGe BiCMOS realization of NMOS, PMOS, and *n-p-n* device. (b) photodiode in BiCMOS, where the N+ buried layer is utilized as screen terminal which blocks slow bulk carriers to high field region. (c) photodiode in CMOS SOI, where the insulator layer (i.e. oxide) acts as the screen terminal.

S.M. Csutak, B. Yang, *et al.* presented several interesting papers [49, 50, 51] which reported the monolithically integrated photodiode in CMOS SOI technology.

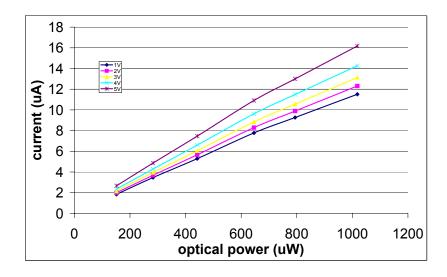

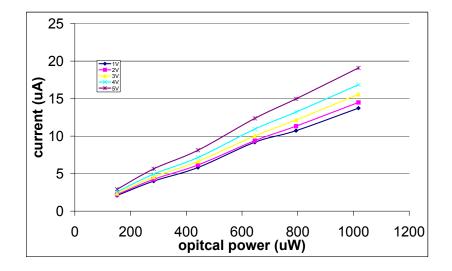

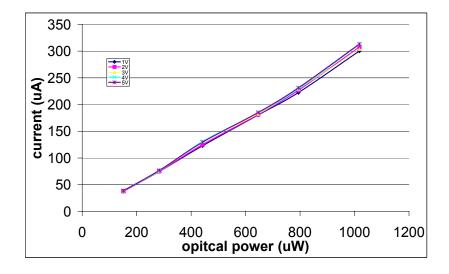

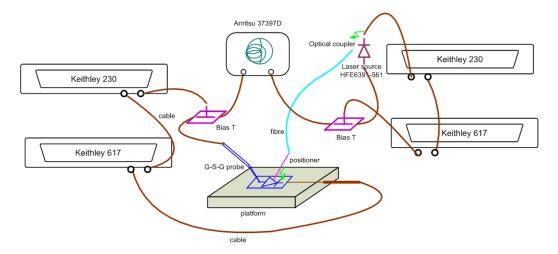

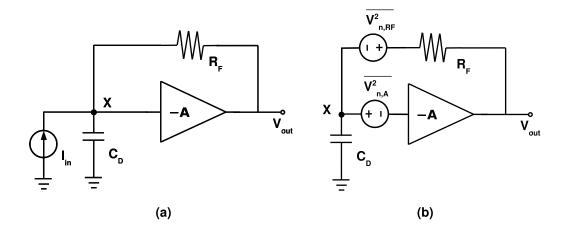

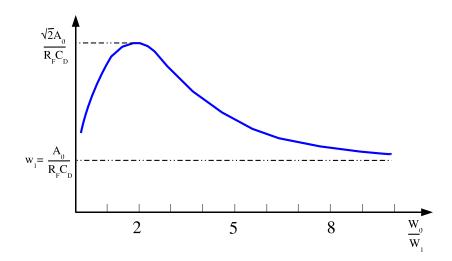

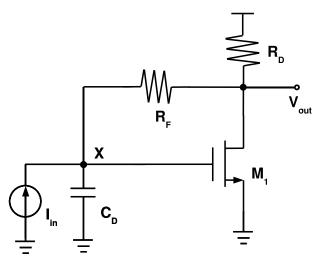

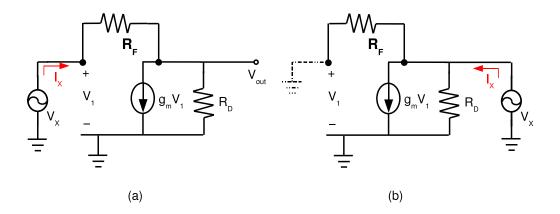

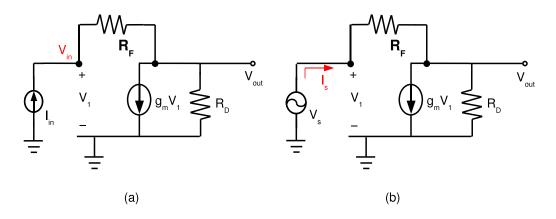

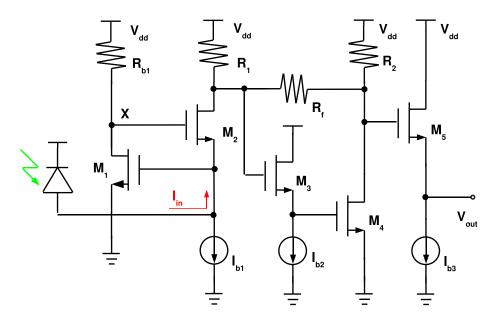

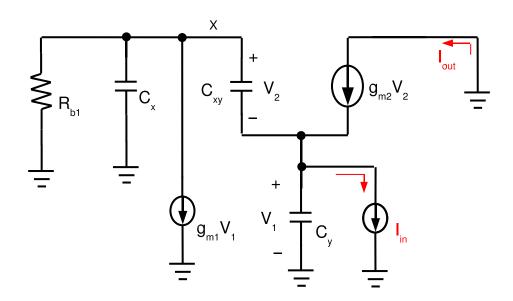

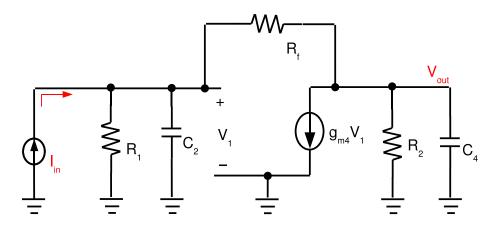

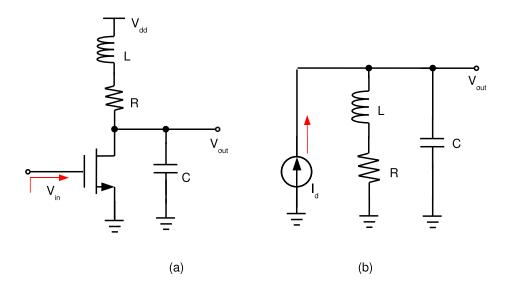

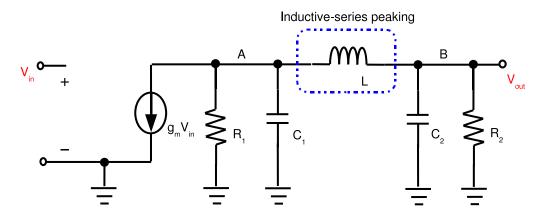

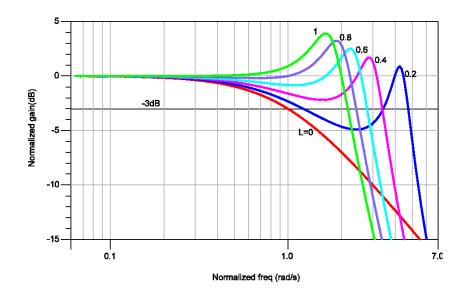

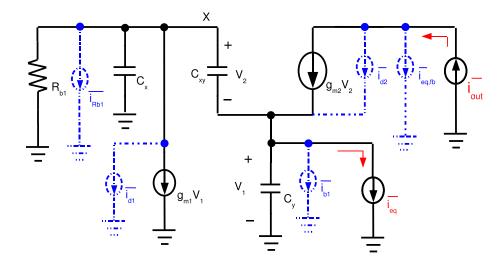

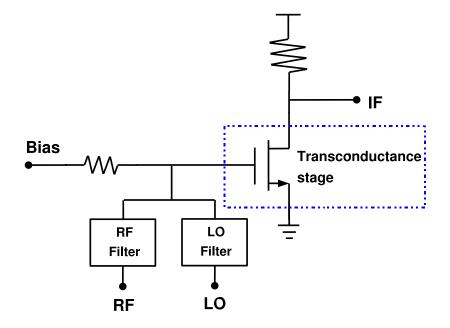

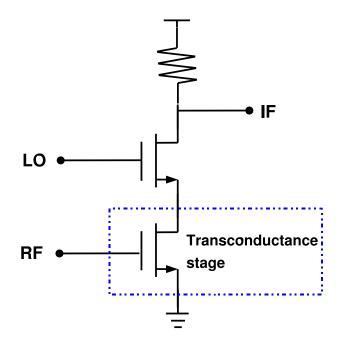

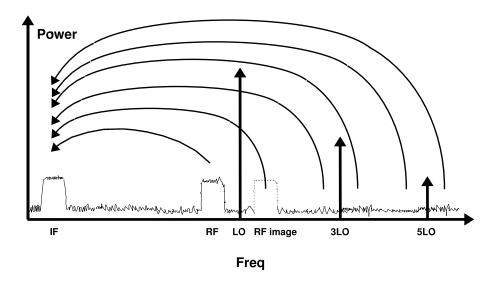

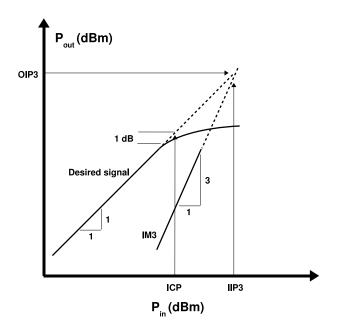

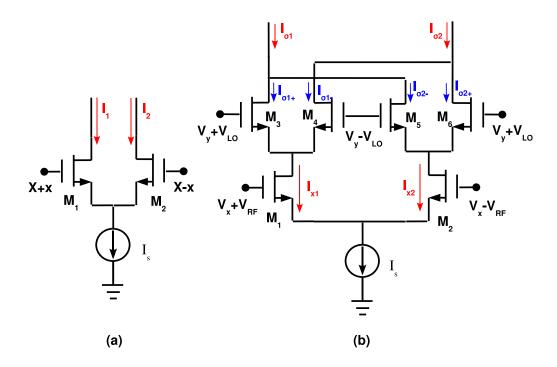

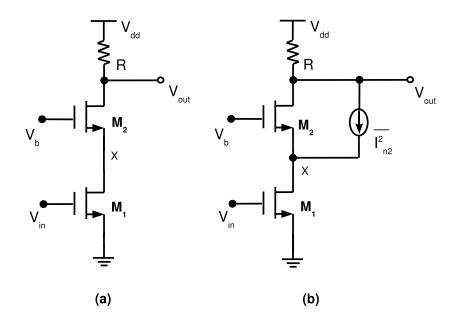

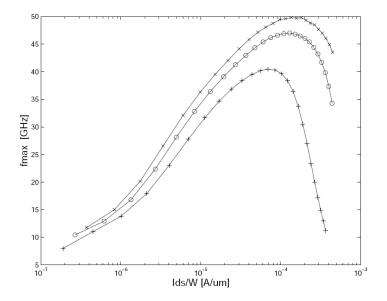

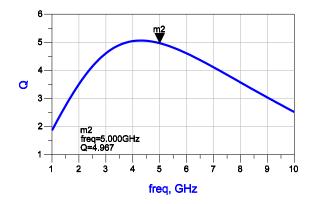

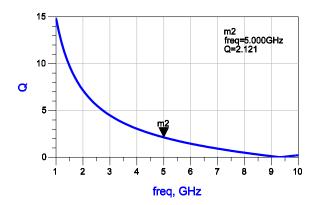

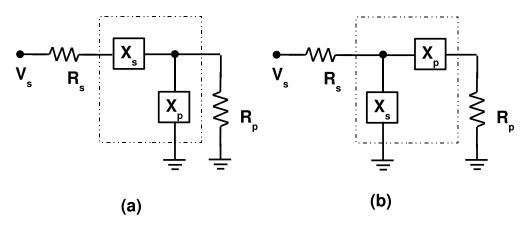

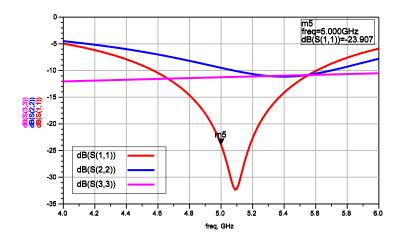

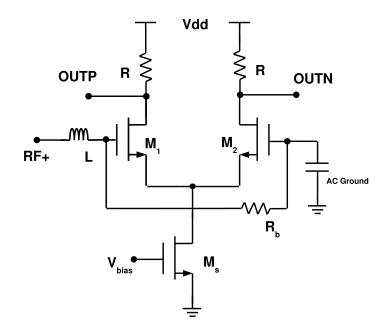

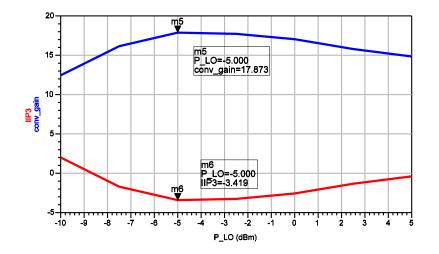

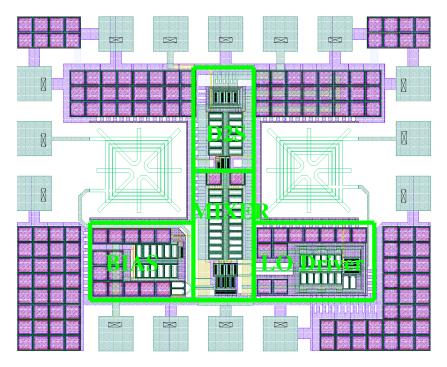

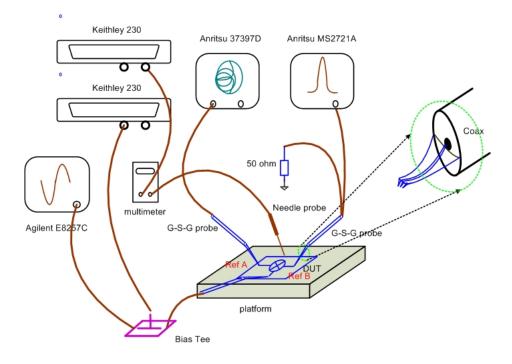

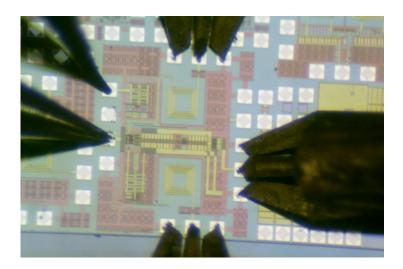

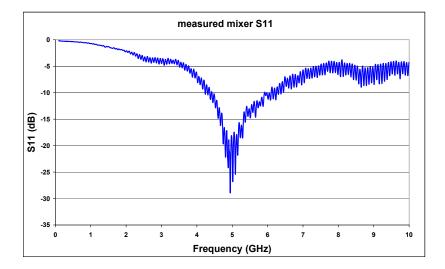

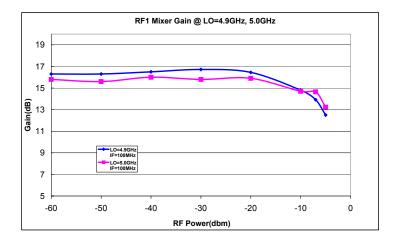

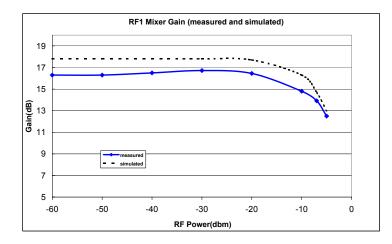

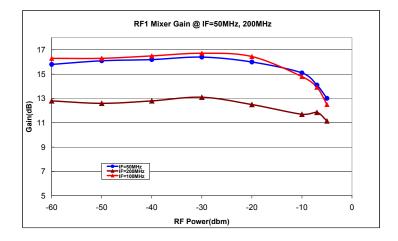

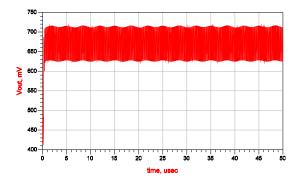

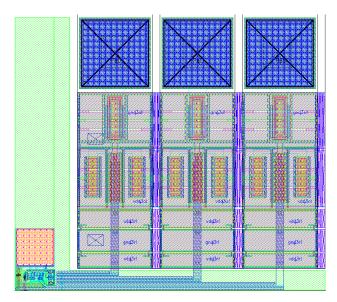

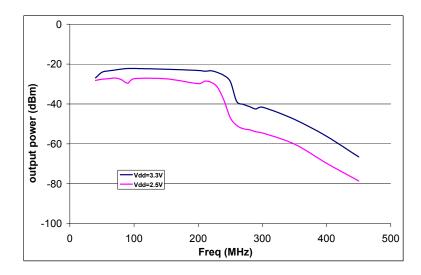

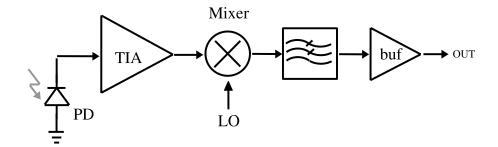

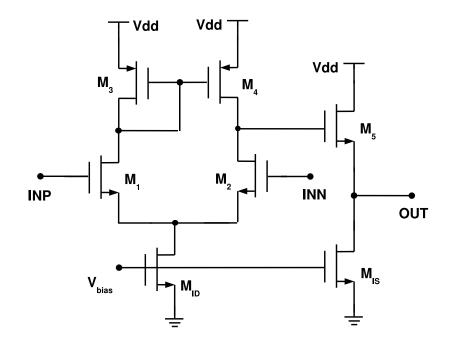

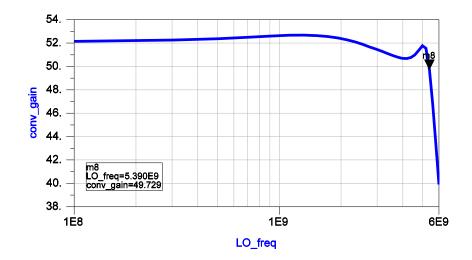

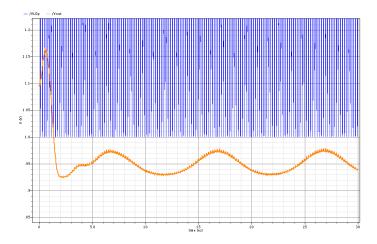

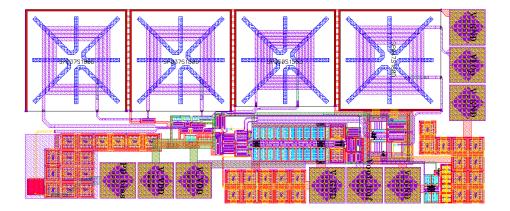

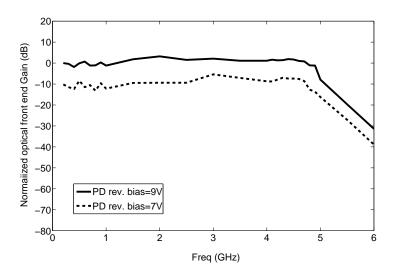

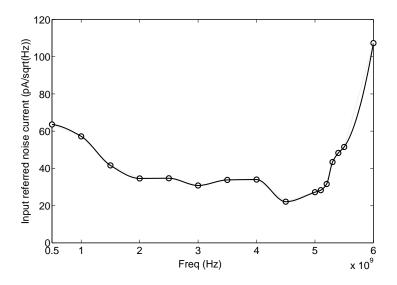

In [51], interdigitated silicon photodiodes fabricated on standard Silicon-On-Insulator substrates with area of 144  $\mu m^2$ , 1  $\mu m \times 0.2 \mu m$  (finger width \* finger spacing), and a 2- $\mu m$ -thick active layer achieved a bandwidth of 8 GHz at 9 V with a peak efficiency of 12% at 850 nm. The devices with the same geometry fabricated on a 200-nm-thick active layer exhibited a 15-GHz bandwidth and 3% quantum efficiency for a reverse bias of 9 V. the simplified cross section of the SOI CMOS technology is shown as Fig. 2.8 (c). Here the screen terminal for the photodetector is the oxide layer which has a similar in function as N+ buried layer in BiCMOS process. In [52] the photodiodes implemented in commercial 130 nm CMOS technology with 2  $\mu m$  SOI substrate achieved -3 dB bandwidth of 8GHz with the optimized area of 50  $\mu m \times 50 \,\mu m$ , finger width and spacing of 2  $\mu m \times 2 \,\mu m$ , but under the reverse bias voltage as high as 28 V.