# Design and Implementation of an Integrating Modulated Light Camera

Roger Alan Light, M.Eng (Hons)

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

June 2008

## Abstract

In optical experiments, replacing the usual constant intensity light source with one that has its intensity modulated at a fixed frequency gives a number of advantages, namely moving the signal of interest away from low frequency noise, allowing the signal to be detected even in the presence of background illumination, as well as being able to gain more information about the experiment by measuring any change in the phase of the modulation.

A number of different types of integrating pixels have been simulated in Matlab with regard to their suitability for use as a modulated light detector, along with different methods for reconstructing the signal. The quadrature method of reconstruction was chosen as the best technique, where four samples are taken per modulated time period then all four samples are used in the I and Q channels of the demodulator.

A modulated light detector has been implemented using a custom integrated circuit in a standard  $0.35\,\mu\mathrm{m}$  CMOS process, linked to a field programmable gate array. The custom circuits consists of a photodiode configured as an integrating type pixel, where the output of the pixel is connected to a comparator so that when coupled with a counter, the pixel can measure the amount of time taken for the photodiode to reach a particular voltage.

A camera with 128 x 128 pixels has been implemented and characterised using a modulated laser as the input, with the results obtained compared to the Matlab simulations carried out. Images have been taken with the camera that show the

camera is able to detect modulated light signals at a modulation depth of 1.39% and modulation frequency of  $420\,\mathrm{Hz}$ . The camera has also been operated successfully for a modulation frequency of  $2.5\,\mathrm{kHz}$ .

# Acknowledgements

I would like to sincerely thank my supervisors Dr. Barrie Hayes-Gill and Dr. John Crowe for their continued support and guidance along the course of this work.

I would also like to thank Ian Stockford for his invaluable help on setting up optical experiments, John Himsworth for his help in obtaining some of the comparator results in Chapter 6 and all of my other colleagues who have helped in other ways, especially those who have hassled me about getting this finished.

This work has been financially supported by the Engineering and Physical Sciences Research Council (EPSRC), UK and the School of Electrical and Electronic Engineering at the University of Nottingham.

Finally, I would like to thank my friends for their support and for putting up with me during the more difficult parts of this work.

# Contents

| $\mathbf{A}$     | bstra        | ct       |              |                                                              | 1     |

|------------------|--------------|----------|--------------|--------------------------------------------------------------|-------|

| $\mathbf{A}_{0}$ | cknov        | m wledge | ${ m ments}$ |                                                              | iii   |

| C                | onter        | its      |              |                                                              | iv    |

| Li               | st of        | Figure   | es           |                                                              | xvii  |

| Li               | st of        | Tables   | 5            | 2                                                            | cviii |

| 1                | $_{ m Intr}$ | oducti   | on           |                                                              | 1     |

|                  | 1.1          | Introd   | uction       |                                                              | 1     |

|                  | 1.2          | Projec   | t Aims .     |                                                              | 1     |

|                  | 1.3          | A Brie   | ef History   | of Photography                                               | 2     |

|                  | 1.4          | Electr   | onic Photo   | $\operatorname{odetection}$                                  | 6     |

|                  |              | 1.4.1    | Optical A    | Absorption in Semiconductors                                 | 7     |

|                  |              | 1.4.2    | CMOS P       | hotodiode                                                    | 11    |

|                  |              |          | 1.4.2.1      | N-Diffusion to $P$ -Substrate                                | 12    |

|                  |              |          | 1.4.2.2      | N-Well to $P$ -Substrate                                     | 12    |

|                  |              |          | 1.4.2.3      | $N	ext{-Well to }P	ext{-Diffusion}$ / Buried Double Junction | 12    |

|                  |              | 1.4.3    | CMOS P       | hototransistor                                               | 14    |

|          |     | 1.4.4 CMOS Photogate              | 15 |

|----------|-----|-----------------------------------|----|

|          |     | 1.4.5 Charge Coupled Device (CCD) | 16 |

|          | 1.5 | CMOS Pixel Sensors                | 16 |

|          |     | 1.5.1 Passive Pixel Sensor        | 16 |

|          |     | 1.5.2 Active Pixel Sensor         | 18 |

|          |     | 1.5.3 Linear Pixel                | 19 |

|          |     | 1.5.4 Logarithmic Pixel           | 21 |

|          |     | 1.5.5 Feedback Pixel              | 22 |

|          | 1.6 | Noise                             | 22 |

|          |     | 1.6.1 Thermal Noise               | 23 |

|          |     | 1.6.2 Shot Noise                  | 24 |

|          |     | 1.6.3 Flicker Noise (1/f) $\dots$ | 26 |

|          |     | 1.6.4 Dark Current                | 27 |

|          |     | 1.6.5 Fixed Pattern Noise         | 28 |

|          |     | 1.6.6 Reset Noise                 | 30 |

|          |     | 1.6.7 Noise Reduction             | 30 |

|          | 1.7 | Summary and Thesis Layout         | 31 |

| <b>2</b> | Mod | dulated Light Camera Review       | 33 |

| _        |     |                                   |    |

|          | 2.1 | Introduction                      | 33 |

|          | 2.2 | CCD Lock-In Cameras               | 33 |

|          |     | 2.2.1 Stenflo                     | 33 |

|          |     | 2.2.2 Spirig                      | 36 |

|          |     | 2.2.3 Lange                       | 36 |

|          | 2.3 | CMOS Integrating Cameras          | 38 |

|   |      | 2.3.1   | Ando                               | 38 |

|---|------|---------|------------------------------------|----|

|   |      | 2.3.2   | Schwarte                           | 40 |

|   |      | 2.3.3   | Ohta                               | 43 |

|   |      | 2.3.4   | Oike                               | 44 |

|   | 2.4  | Contin  | uous Time CMOS Cameras             | 46 |

|   |      | 2.4.1   | Benten                             | 46 |

|   |      | 2.4.2   | Bourquin                           | 48 |

|   |      | 2.4.3   | Ducros                             | 49 |

|   |      | 2.4.4   | Lu                                 | 50 |

|   |      | 2.4.5   | Pitter                             | 52 |

|   |      | 2.4.6   | Dmochowski                         | 54 |

|   | 2.5  | Other   | Cameras                            | 55 |

|   |      | 2.5.1   | Ma                                 | 56 |

|   |      | 2.5.2   | Kleinfelder                        | 57 |

|   | 2.6  | Compa   | arison of Cameras                  | 60 |

|   | 2.7  | Summa   | ary                                | 61 |

| 3 | Lock | k-In Tl | neory                              | 62 |

|   | 3.1  |         | action                             | 62 |

|   | 3.2  | Ration  | ale Behind Modulation              | 63 |

|   |      | 3.2.1   | Modulation in Voice Communications | 63 |

|   |      | 3.2.2   | Modulation in Optical Experiments  | 63 |

|   | 3.3  | Types   | of Modulation                      | 64 |

|   |      | 3.3.1   |                                    | 64 |

|   |      | 3.3.2   | <u>-</u>                           |    |

|   |      |         |                                    |    |

|      | 3.3.3   | Frequency Modulation (FM)           | 65  |

|------|---------|-------------------------------------|-----|

| 3.4  | Ampli   | tude Modulation Theory              | 66  |

|      | 3.4.1   | Modulation                          | 66  |

|      | 3.4.2   | Demodulation                        | 68  |

|      | 3.4.3   | Quadrature Demodulation             | 70  |

| 3.5  | Democ   | dulation in Practice                | 72  |

|      | 3.5.1   | Sampling                            | 73  |

|      | 3.5.2   | Digitisation                        | 74  |

|      | 3.5.3   | Sampling After Filtering            | 75  |

|      | 3.5.4   | Sampling After Mixing               | 75  |

|      | 3.5.5   | Sampling Before Mixing              | 79  |

|      | 3.5.6   | Sampling to Simplify Mixing         | 82  |

| 3.6  | Modul   | ated Light Camera Parameters        | 87  |

| 3.7  | Compa   | arison of Existing Work             | 88  |

| 3.8  | Integra | ating Lock-In                       | 89  |

| 3.9  | Compa   | arison of Techniques                | 91  |

|      | 3.9.1   | Matlab Model                        | 91  |

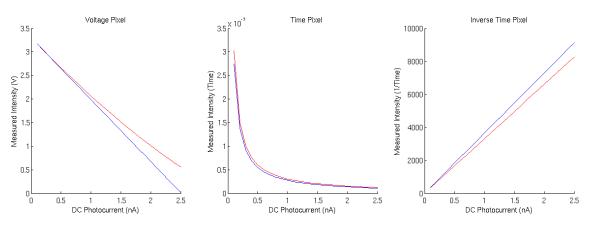

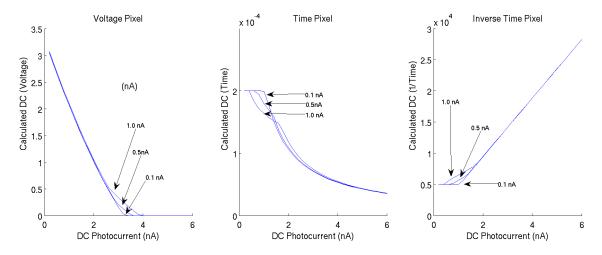

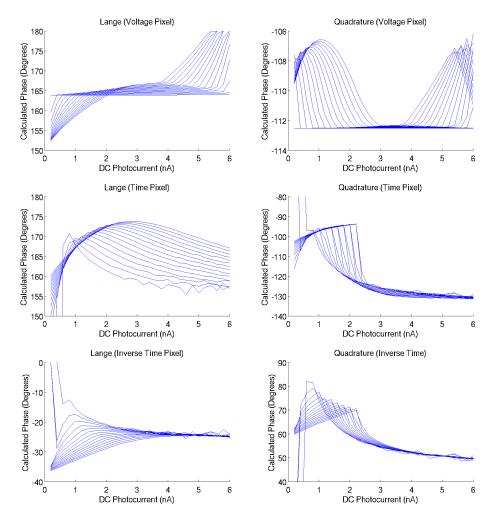

|      | 3.9.2   | DC Response                         | 93  |

|      | 3.9.3   | Two Phase Pixel DC Response         | 93  |

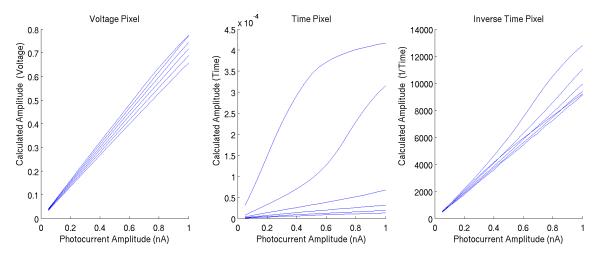

|      | 3.9.4   | Two Phase Pixel Amplitude Response  | 95  |

|      | 3.9.5   | Two Phase Pixel Frequency Response  | 95  |

|      | 3.9.6   | Four Phase Pixel DC Response        | 97  |

|      | 3.9.7   | Four Phase Pixel Amplitude Response | 97  |

|      | 3.9.8   | Four Phase Pixel Phase Response     | 100 |

|      | 3.9.9   | Four Phase Pixel Frequency Response | 102 |

| 3 10 | Summ    | arv                                 | 105 |

| 4 | Pix | el Designs 107                     |

|---|-----|------------------------------------|

|   | 4.1 | Introduction                       |

|   | 4.2 | Architecture                       |

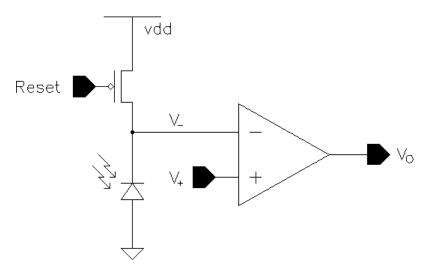

|   | 4.3 | Comparator Design                  |

|   |     | 4.3.1 Operation and Non-Idealities |

|   |     | 4.3.2 Simple Comparator            |

|   |     | 4.3.3 Comparator with Hysteresis   |

|   |     | 4.3.3.1 Output Stage               |

|   | 4.4 | Chip One - MLCv2                   |

|   |     | 4.4.1 Overall Design               |

|   |     | 4.4.2 Front End Circuit            |

|   |     | 4.4.2.1 NMOS Switch                |

|   |     | 4.4.2.2 PMOS Switch                |

|   |     | 4.4.2.3 CMOS Switch                |

|   |     | 4.4.2.4 Conclusion                 |

|   |     | 4.4.3 Photodiode                   |

|   |     | 4.4.4 Comparator                   |

|   |     | 4.4.5 Source Follower              |

|   |     | 4.4.6 Final Pixel                  |

|   | 4.5 | Chip Two - PC2                     |

|   |     | 4.5.1 Pixel                        |

|   |     | 4.5.2 Array                        |

|   | 4.6 | Chip Three - PC3                   |

|   | 4.7 | Results                            |

|   | 4.8 | Summary                            |

| 5 | Car | nera Design                             | 139   |

|---|-----|-----------------------------------------|-------|

|   | 5.1 | Introduction                            | . 139 |

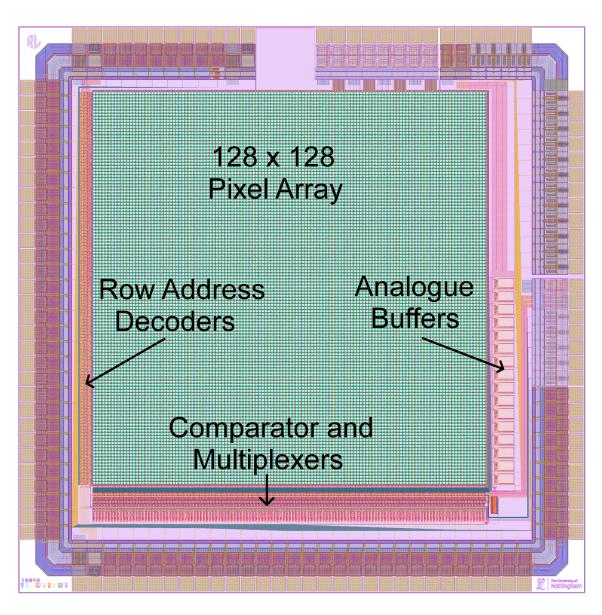

|   | 5.2 | Camera Architecture                     | . 140 |

|   | 5.3 | Front End and Photodiode                | . 147 |

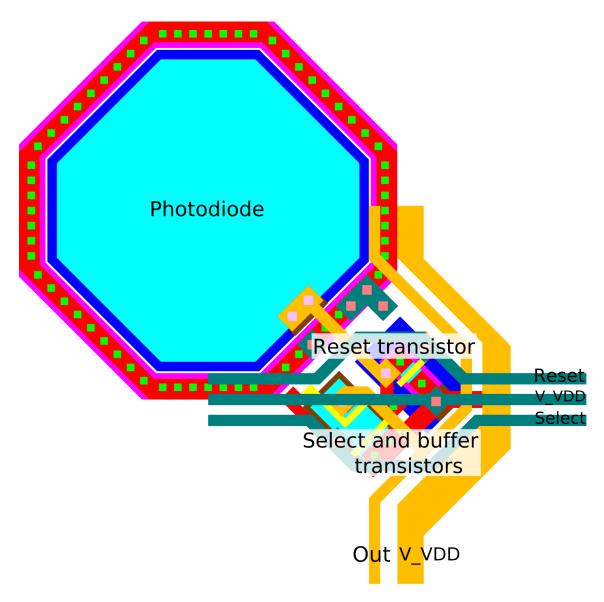

|   |     | 5.3.1 Source Follower and Select Switch | . 147 |

|   |     | 5.3.2 Photodiode                        | . 148 |

|   |     | 5.3.3 Final Pixel                       | . 149 |

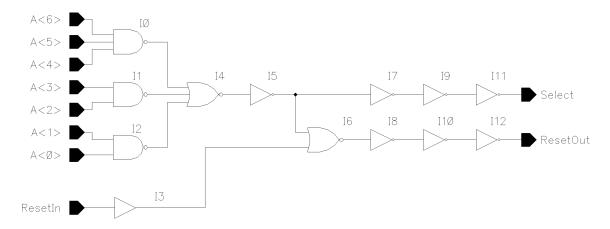

|   | 5.4 | Array Row Address and Reset Decoders    | . 151 |

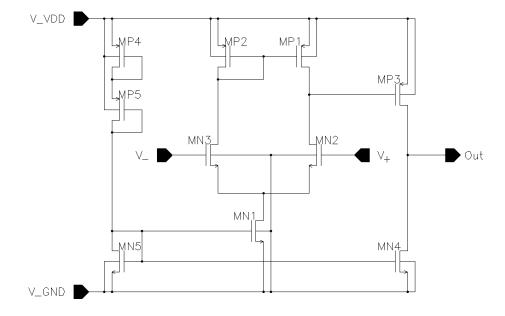

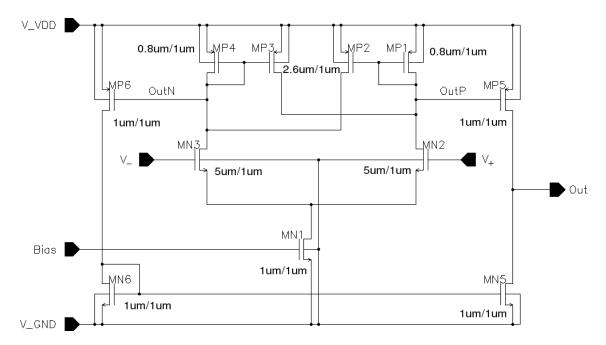

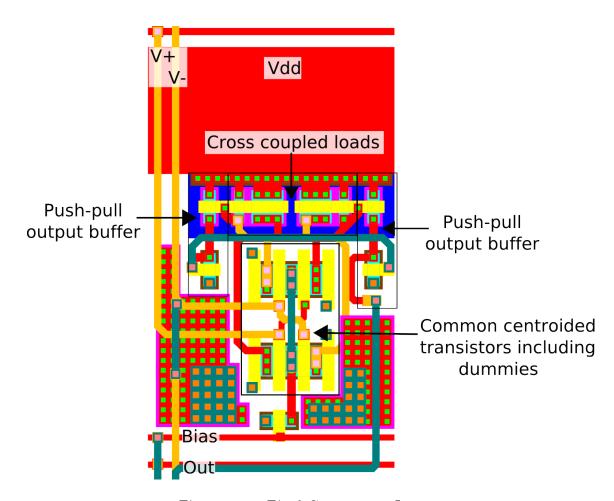

|   | 5.5 | Comparator Design                       | . 153 |

|   |     | 5.5.1 Final Design                      | . 153 |

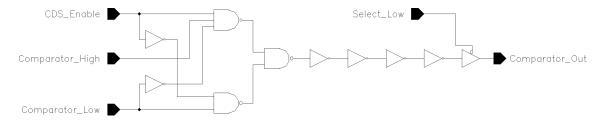

|   | 5.6 | Comparator Output Multiplexer           | . 157 |

|   | 5.7 | Analogue Outputs                        | . 161 |

|   | 5.8 | Camera Summary                          | . 161 |

|   | 5.9 | Digital Processing                      | . 164 |

|   |     | 5.9.1 Platform                          | . 164 |

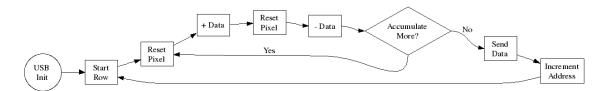

|   |     | 5.9.2 Basic Principle                   | . 164 |

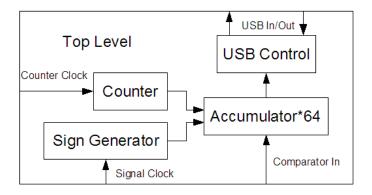

|   |     | 5.9.3 Architecture                      | . 165 |

|   |     | 5.9.3.1 Top Level Module                | . 165 |

|   |     | 5.9.3.2 USB Control                     | . 166 |

|   |     | 5.9.3.3 Counter                         | . 166 |

|   |     | 5.9.3.4 Accumulators                    | . 166 |

|   |     | 5.9.3.5 Sign Generator                  | . 168 |

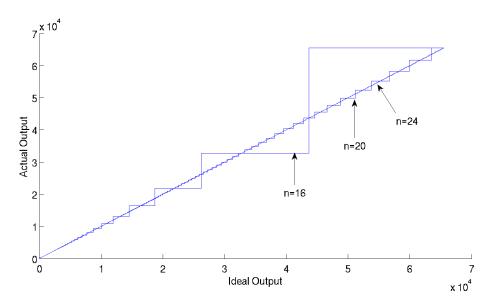

|   |     | 5.9.3.6 Inverting Counter               | . 168 |

|   |     | 5.9.3.7 Linear Counter with Divider     | . 170 |

|   |      |             | 5.9.3.8 Lookup Table         |

|---|------|-------------|------------------------------|

|   |      |             | 5.9.3.9 Reduced Lookup Table |

|   |      | 5.9.4       | Final Designs                |

|   | 5.10 | Summ        | ary                          |

| 6 | Res  | ${ m ults}$ | 175                          |

|   | 6.1  | Introd      | iction                       |

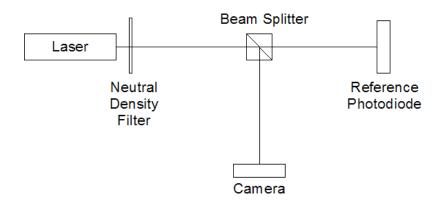

|   | 6.2  | Camer       | a Experimental Setup         |

|   | 6.3  | DC Re       | sults                        |

|   | 6.4  | Two P       | hase Results                 |

|   |      | 6.4.1       | Amplitude Response           |

|   |      | 6.4.2       | Phase Response               |

|   |      | 6.4.3       | Frequency Response           |

|   | 6.5  | Four I      | hase Results                 |

|   |      | 6.5.1       | Amplitude Response           |

|   |      | 6.5.2       | Phase Response               |

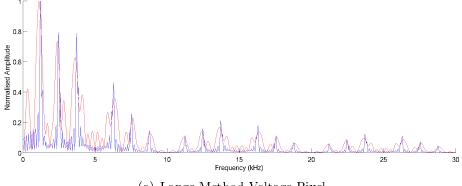

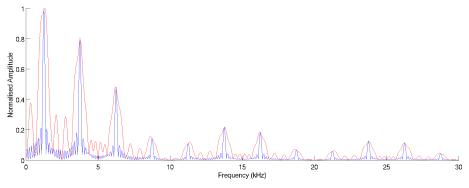

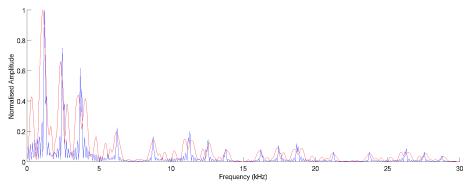

|   |      | 6.5.3       | Frequency Response           |

|   |      | 6.5.4       | Correlated Double Sampling   |

|   | 6.6  | Image       | Results                      |

|   |      | 6.6.1       | Setup                        |

|   |      | 6.6.2       | DC Image Results             |

|   |      | 6.6.3       | Two Phase Image Results      |

|   |      | 6.6.4       | Four Phase Image Results     |

|   | 6.7  | Fixed       | Pattern Noise                |

|   | 6.8  | Summ        | 108                          |

| 7            | Disc  | cussion and Conclusions  | 200   |

|--------------|-------|--------------------------|-------|

|              | 7.1   | Introduction             | . 200 |

|              | 7.2   | Thesis Summary           | . 200 |

|              | 7.3   | Further Discussion       | . 202 |

| Bi           | bliog | graphy                   | 207   |

| $\mathbf{A}$ | Mat   | tlab Pixel Models        | 214   |

|              | A.1   | Voltage Pixel            | . 214 |

|              | A.2   | Time Pixel               | . 216 |

|              | A.3   | N-Well Diode Leakage     | . 217 |

|              | A.4   | N-Well Diode Capacitance | . 218 |

# List of Figures

| 1.1  | First Colour Photo, by James Clerk Maxwell    | 2  |

|------|-----------------------------------------------|----|

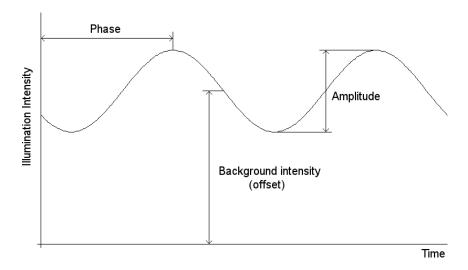

| 1.2  | Modulated Light Parameters                    | 4  |

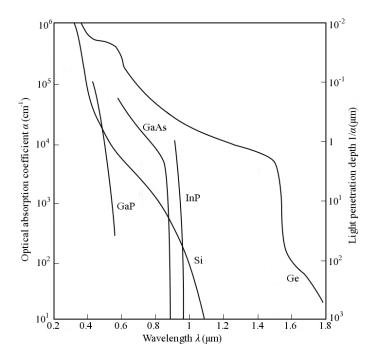

| 1.3  | Semiconductor Absorption Coefficients         | 9  |

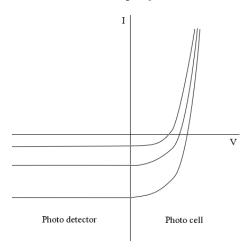

| 1.4  | Illuminated $pn$ Junction I-V Characteristics | 10 |

| 1.5  | N-Diffusion to $P$ -Substrate Diode           | 12 |

| 1.6  | N-Well to $P$ -Substrate Diode                | 13 |

| 1.7  | N-Well to $P$ -Diffusion Diode                | 13 |

| 1.8  | Bipolar Photo Transistor Cross Sections       | 15 |

| 1.9  | Photogate                                     | 16 |

| 1.10 | PPS Schematic                                 | 17 |

| 1.11 | Three Transistor APS Schematic                | 18 |

| 1.12 | Four Transistor Shutter APS Schematic         | 20 |

| 1.13 | Linear Pixel Schematic                        | 20 |

| 1.14 | Logarithmic Pixel Schematic                   | 22 |

| 1.15 | Feedback Pixel Schematic                      | 23 |

| 1.16 | Oxide-Silicon Interface                       | 26 |

| 1.17 | Flicker Noise Corner Frequency                | 27 |

| 1.18 | Example of FPN                                | 29 |

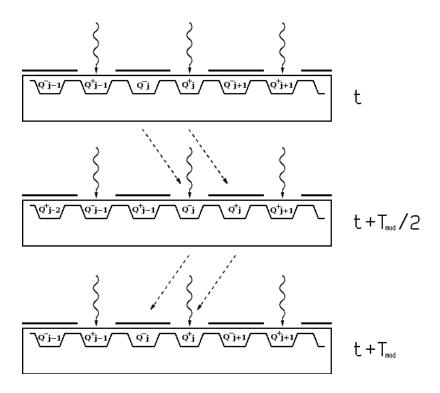

| 2.1  | Two Phase CCD Demodulation                                                                | 35 |

|------|-------------------------------------------------------------------------------------------|----|

| 2.2  | Three Phase Correlation Image Sensor                                                      | 39 |

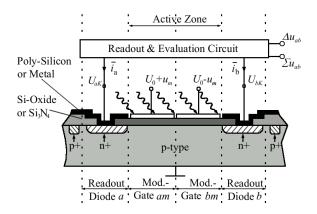

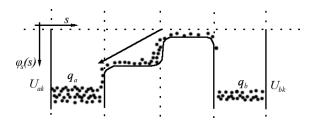

| 2.3  | PMD Pixel Cross Section                                                                   | 40 |

| 2.4  | PMD Pixel Operation                                                                       | 41 |

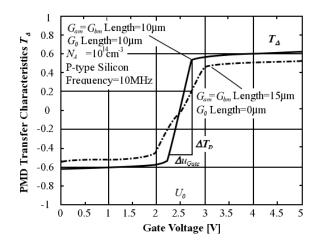

| 2.5  | 2 Gate PMD and 3 Gate PMD Charge Transfer Characteristics $$                              | 42 |

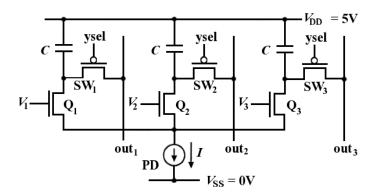

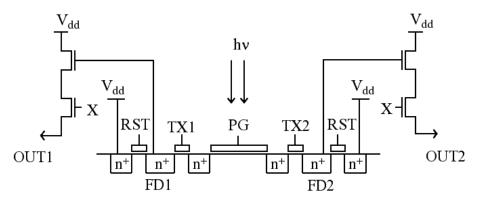

| 2.6  | Demodulation Pixel Circuit                                                                | 43 |

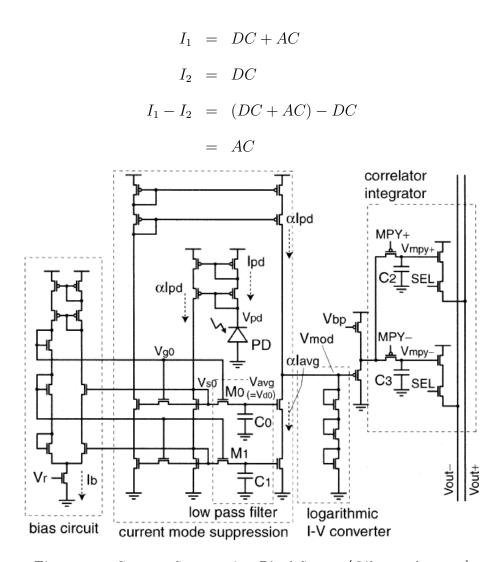

| 2.7  | Current Suppression Pixel Sensor                                                          | 45 |

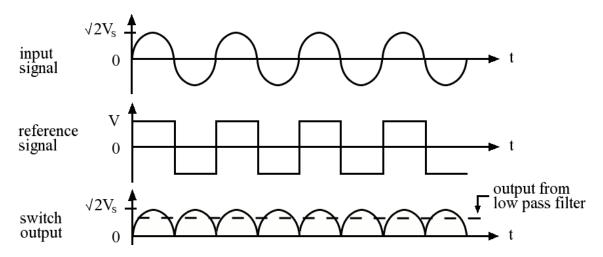

| 2.8  | Switching Multiplier Operation                                                            | 47 |

| 2.9  | Smart Detector Pixel Schematic                                                            | 49 |

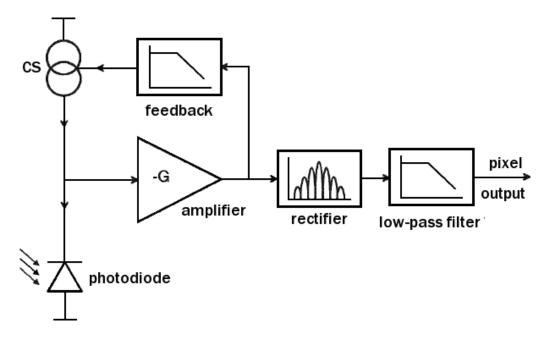

| 2.10 | OCT Image of an Onion                                                                     | 50 |

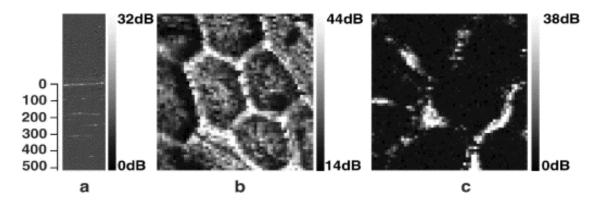

| 2.11 | BDJ Pixel Sensor                                                                          | 51 |

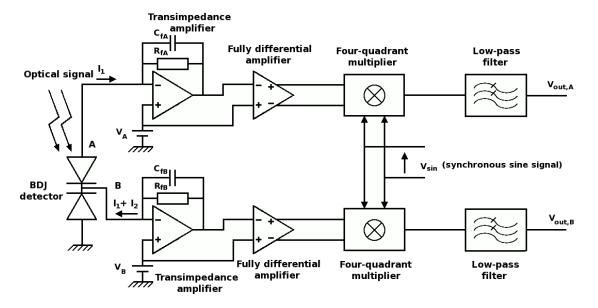

| 2.12 | Modulated Thermoreflectance Pixel Circuit                                                 | 53 |

| 2.13 | Synchronous Pixel Frequency Response                                                      | 55 |

| 2.14 | 2 x 2 DPS Layout                                                                          | 58 |

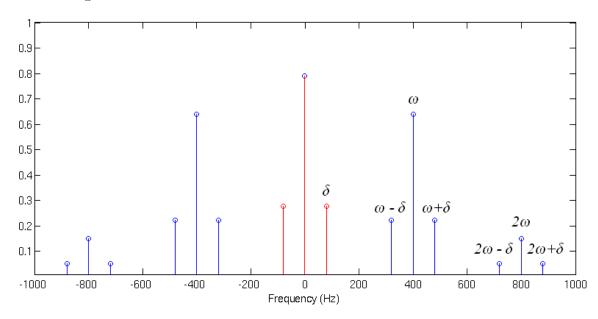

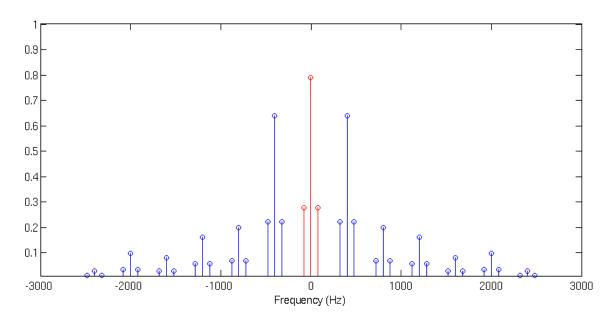

| 3.1  | Amplitude Modulated Frequency Spectrum                                                    | 67 |

| 3.2  | Demodulated AM Frequency Spectrum                                                         | 69 |

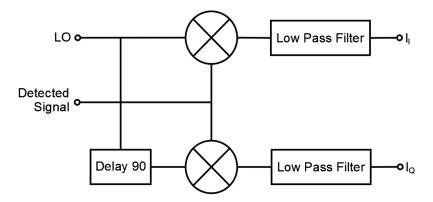

| 3.3  | Quadrature Demodulation                                                                   | 71 |

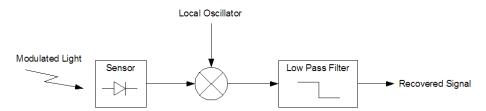

| 3.4  | Simplified Lock-In Sensor                                                                 | 73 |

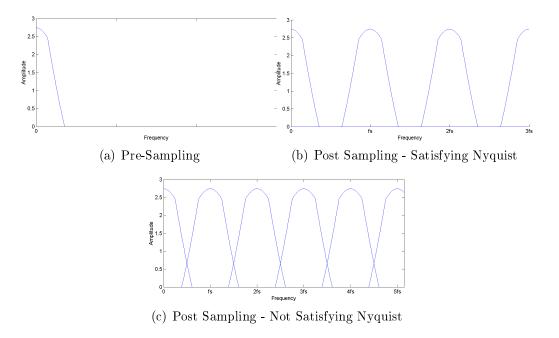

| 3.5  | Sampled Frequency Spectra                                                                 | 74 |

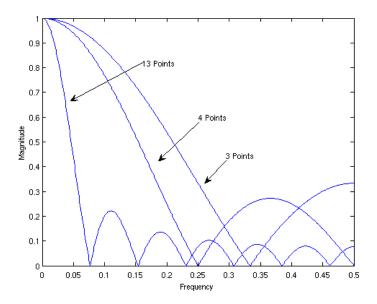

| 3.6  | Moving Average Filter Response                                                            | 77 |

| 3.7  | Square Wave Demodulation Frequency Spectrum                                               | 82 |

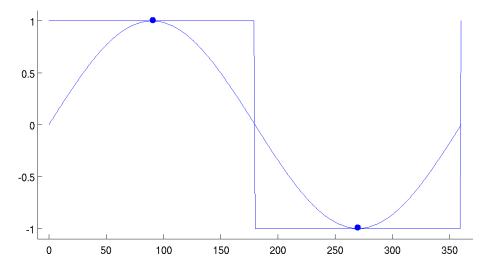

| 3.8  | Local Oscillator Square/Sine Equivalence                                                  | 84 |

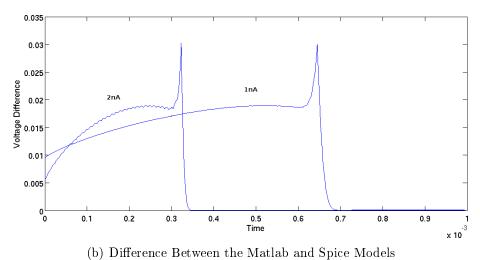

| 3.9  | ${\bf Matlab \ / \ Cadence \ Diode \ Model \ Comparison \ . \ . \ . \ . \ . \ . \ . \ .}$ | 92 |

| 3.10 | DC Pixel Response                                                                         | 93 |

| 3.11 | Two Phase Pixel DC Response                 |

|------|---------------------------------------------|

| 3.12 | Two Phase Pixel Amplitude Response          |

| 3.13 | Two Phase Pixel Frequency Response          |

| 3.14 | Four Phase Pixel Amplitude Response         |

| 3.15 | Four Phase Pixel Amplitude / DC Response    |

| 3.16 | Four Phase Pixel Phase Error                |

| 3.17 | Phase Response to DC Offset                 |

| 3.18 | Four Phase Pixel Frequency Response         |

| 3.19 | Quadrature Voltage Pixel Frequency Response |

| 4.1  | Pixel Architecture                          |

| 4.2  | Differential Pair Comparator                |

| 4.3  | Comparator Response in Noisy Environment    |

| 4.4  | Hysteresis Curve                            |

| 4.5  | Comparator with Hysteresis                  |

| 4.6  | MLCv2 Schematic                             |

| 4.7  | Polysilicon Resistor Spacing                |

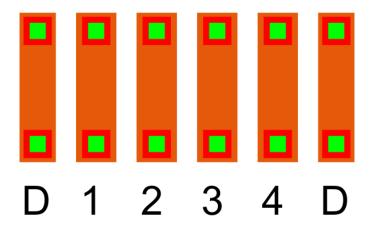

| 4.8  | Polysilicon Resistors with Dummies (D)      |

| 4.9  | One Dimensional Common Centroid Layout      |

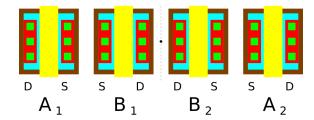

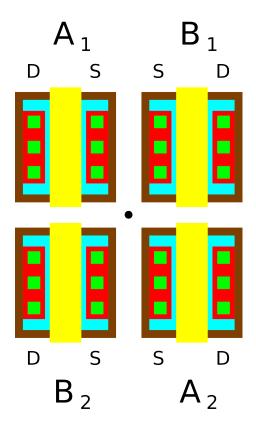

| 4.10 | Two Dimensional Common Centroid Layout      |

| 4.11 | MLCv2 Source Follower Schematic             |

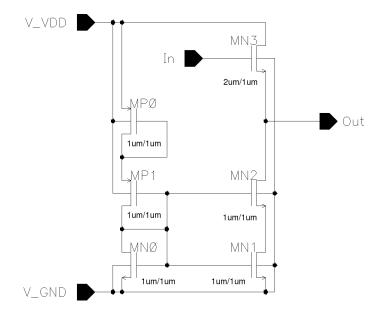

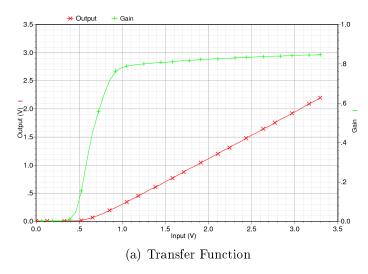

| 4.12 | Source Follower Transfer Function and Gain  |

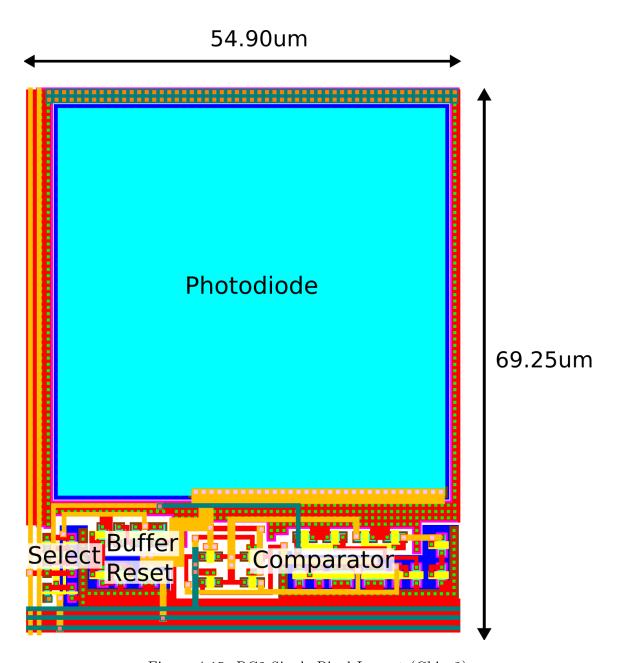

| 4.13 | MLCv2 Pixel Layout (Chip 1)                 |

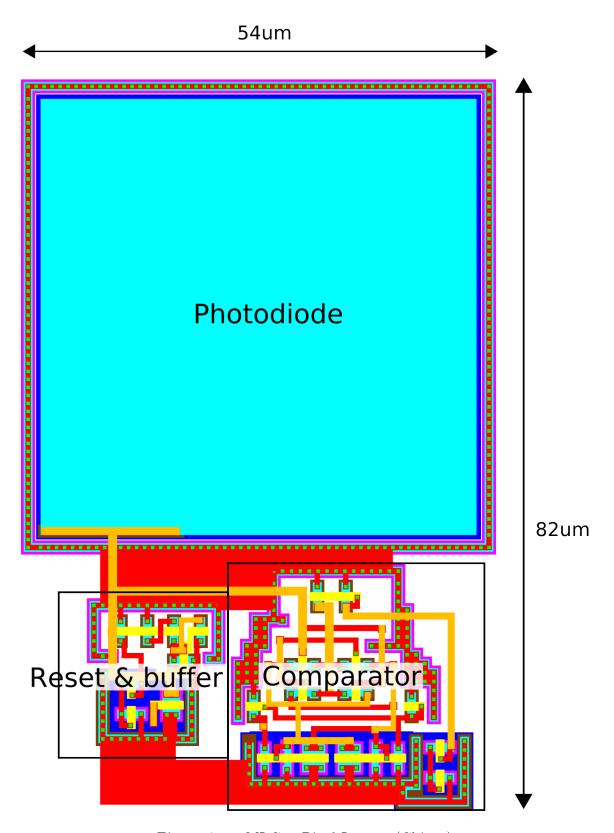

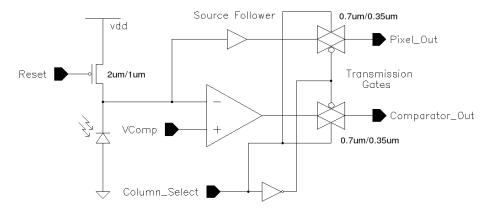

| 4.14 | PC2 Pixel Schematic                         |

| 4.15 | PC2 Single Pixel Layout (Chip 2)            |

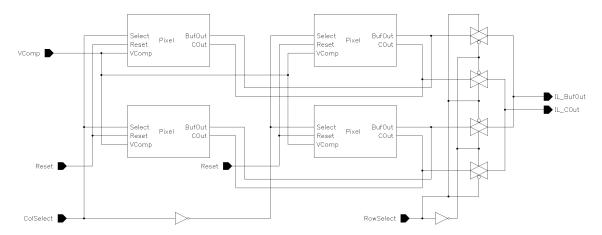

| 4.16 | PC2 Pixel Array Schematic                          |

|------|----------------------------------------------------|

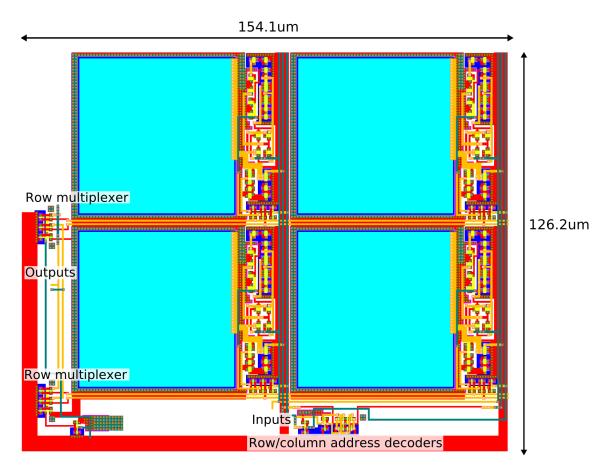

| 4.17 | PC2 Pixel Array Layout                             |

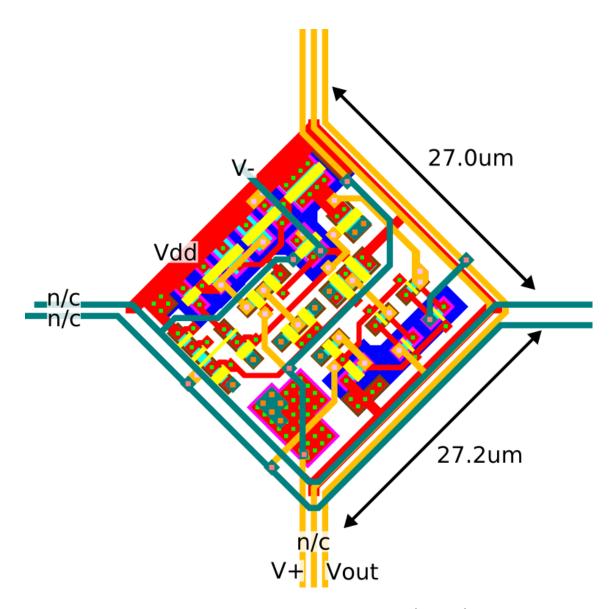

| 4.18 | PC3 Comparator Layout (Chip 3)                     |

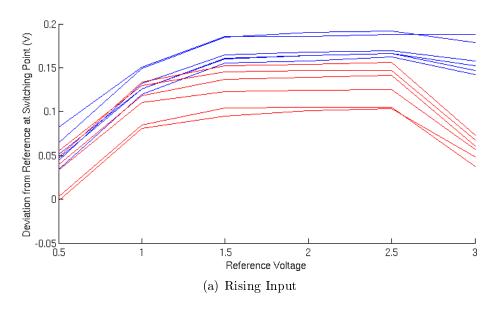

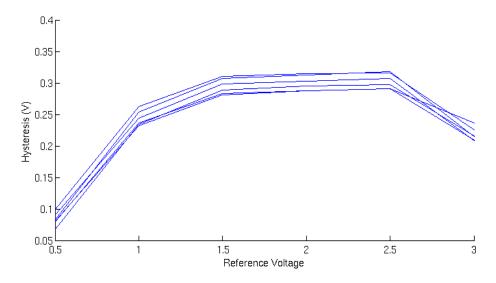

| 4.19 | Comparator Voltage Offsets                         |

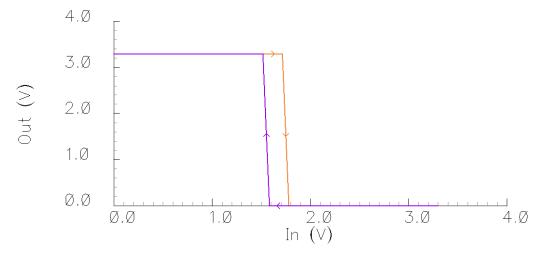

| 4.20 | Comparator Hysteresis                              |

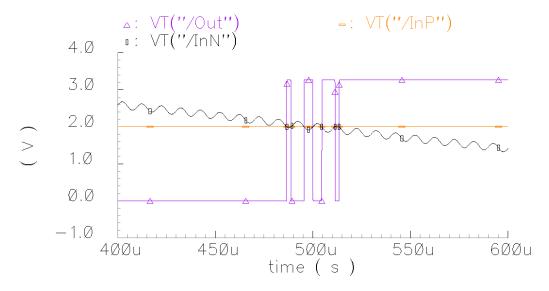

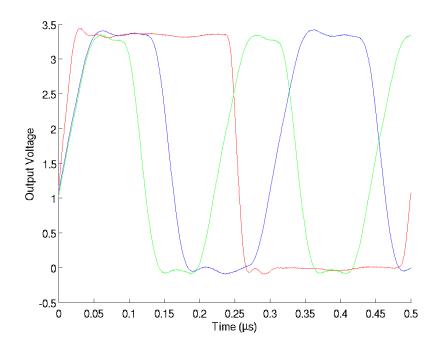

| 4.21 | Comparator Transient Results                       |

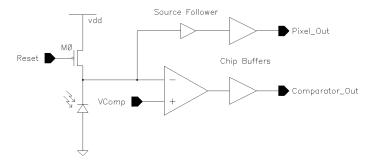

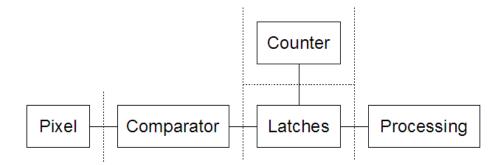

| 5.1  | Pixel Architecture                                 |

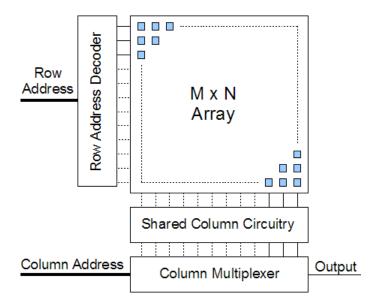

| 5.2  | Column Based Camera Architecture                   |

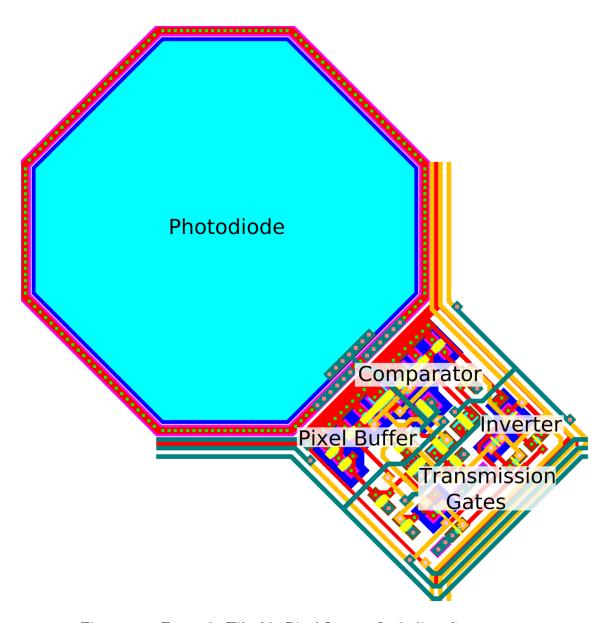

| 5.3  | Example Tileable Pixel Layout Including Comparator |

| 5.4  | Final Pixel Layout                                 |

| 5.5  | Single Row Address and Reset Decoder               |

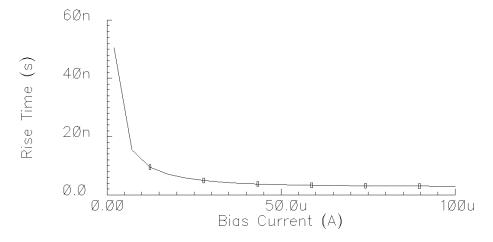

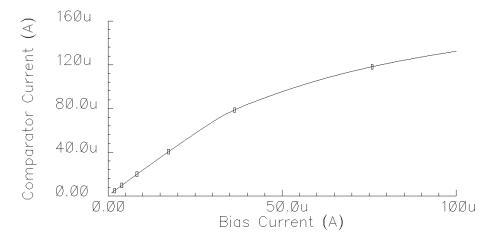

| 5.6  | Comparator Output Rise Time                        |

| 5.7  | Comparator Transient Frequency Comparison          |

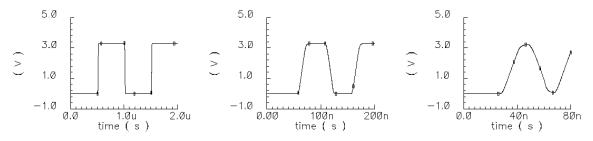

| 5.8  | Comparator Current Consumption                     |

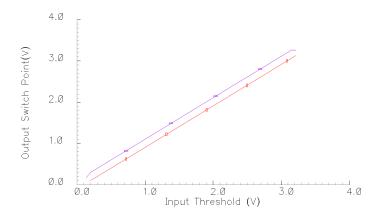

| 5.9  | Comparator Switch Point Simulation                 |

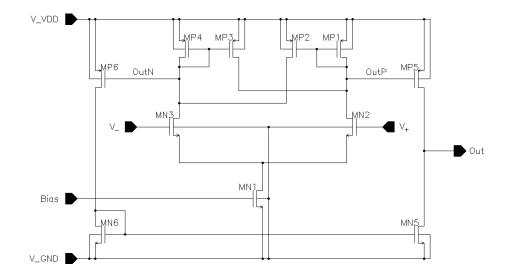

| 5.10 | Final Comparator Schematic                         |

| 5.11 | Final Comparator Layout                            |

| 5.12 | Comparator Output Multiplexer Schematic            |

| 5.13 | 128 x 128 Integrating APS Camera Layout            |

| 5.14 | Basic Two Phase VHDL Flow                          |

| 5.15 | Digital Processing Architecture                    |

| 5.16 | Inverting Counter Response                         |

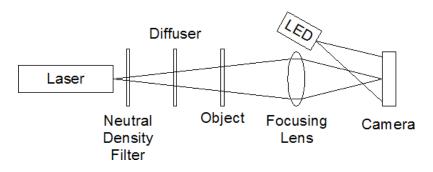

| 6.1  | Experimental Setup                                 |

| 6.2  | Optical Bench Layout                                                             |

|------|----------------------------------------------------------------------------------|

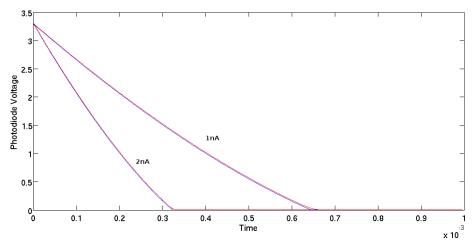

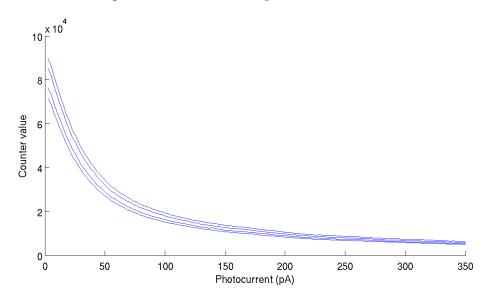

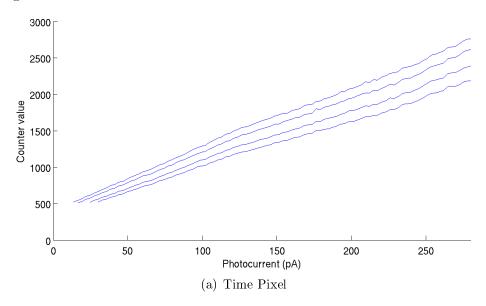

| 6.3  | DC Response (Time Pixel)                                                         |

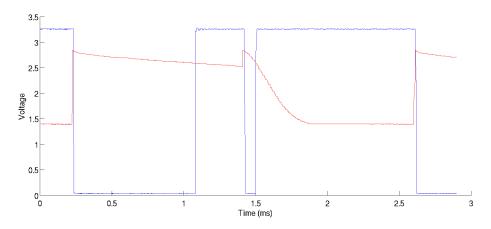

| 6.4  | Pixel and Comparator Waveforms at DC                                             |

| 6.5  | DC Response (Inverse Time Pixel)                                                 |

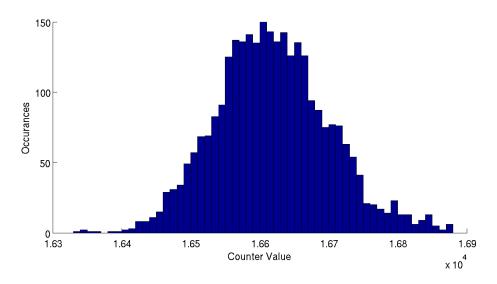

| 6.6  | Read Noise Results                                                               |

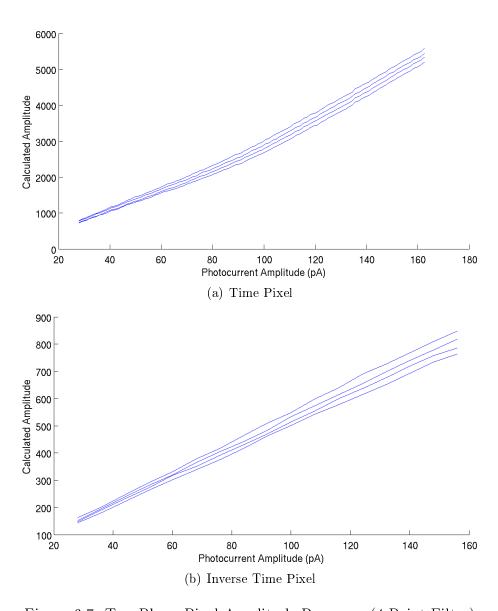

| 6.7  | Two Phase Pixel Amplitude Response (4 Point Filter)                              |

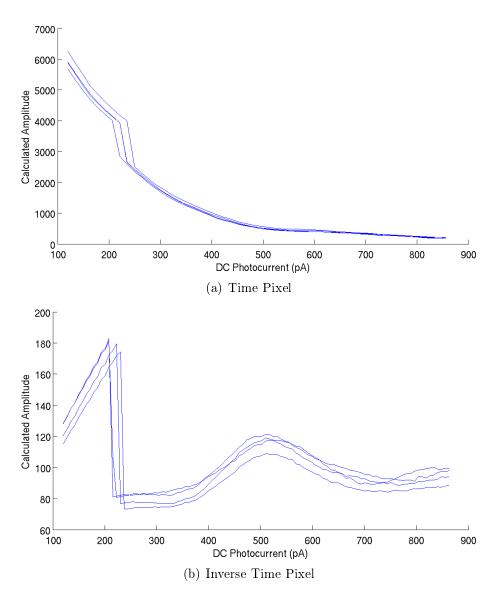

| 6.8  | Two Phase Pixel Amplitude/DC Response (4 Point Filter) $\ \ldots \ \ldots \ 182$ |

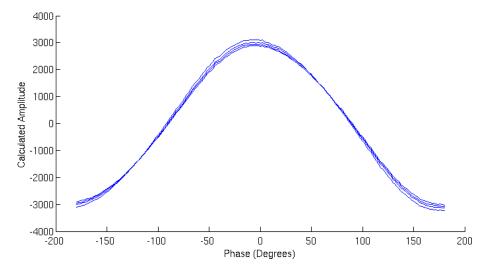

| 6.9  | Two Phase Pixel Phase Response                                                   |

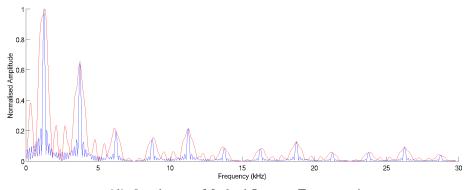

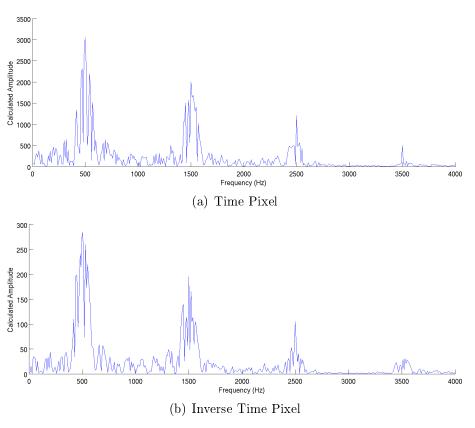

| 6.10 | Two Phase Pixel Frequency Response (Filter Length 4) 184                         |

| 6.11 | Two Phase Pixel Frequency Response (Filter Length 16) 185                        |

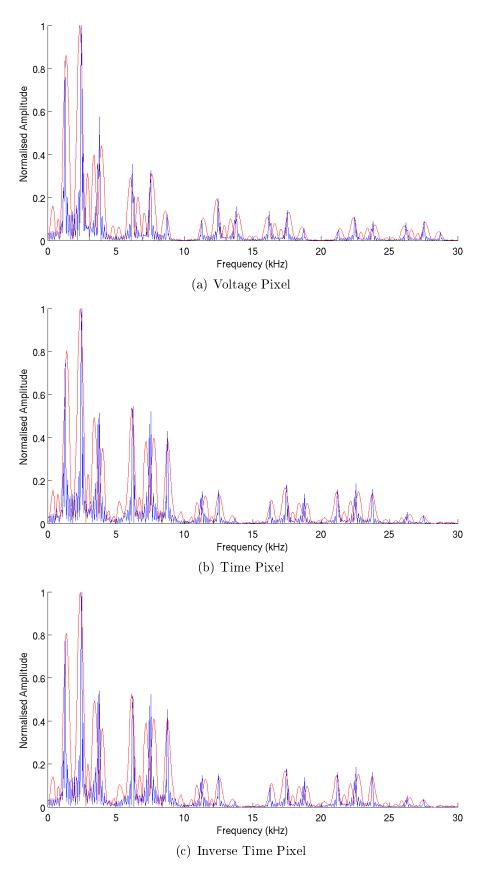

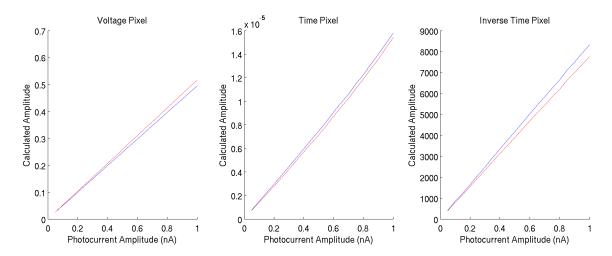

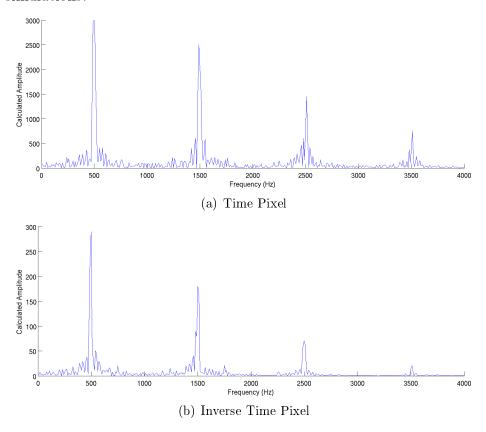

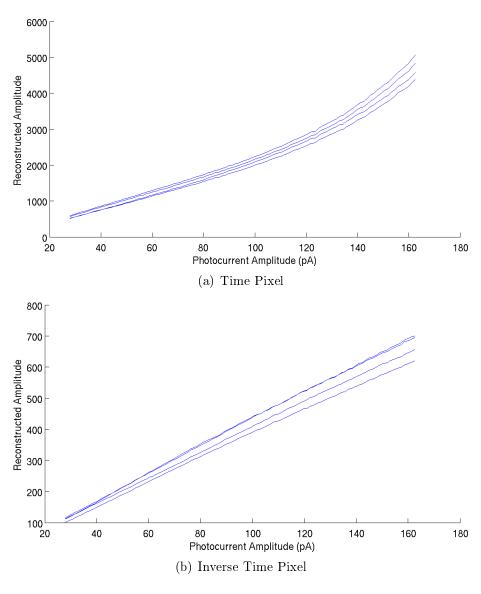

| 6.12 | Four Phase Pixels Amplitude Response                                             |

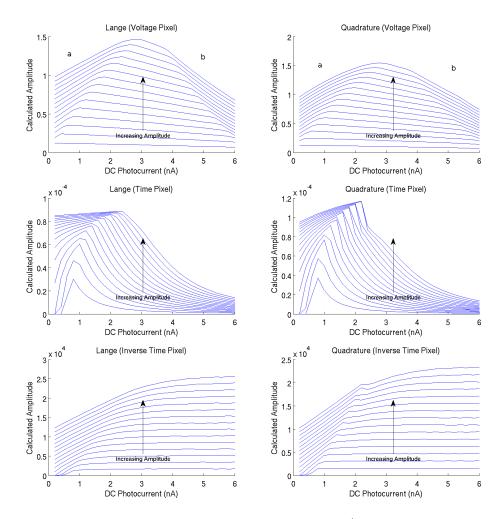

| 6.13 | Four Phase Pixels Amplitude/DC Response                                          |

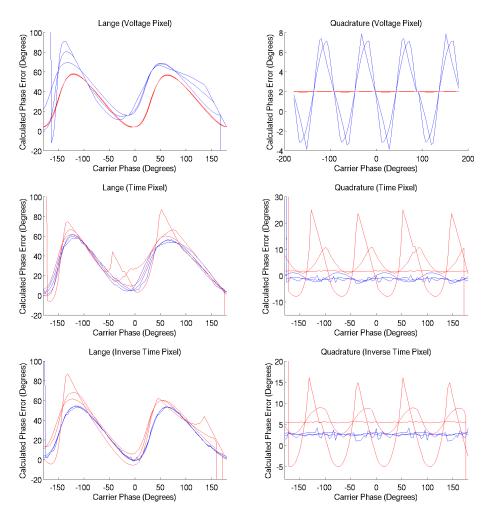

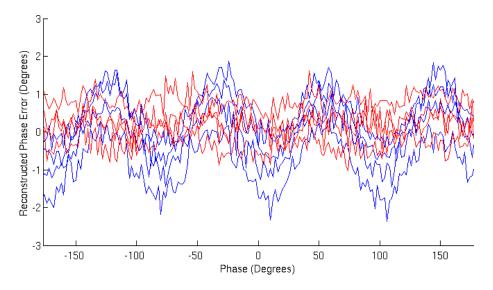

| 6.14 | Four Phase Pixel Phase Response                                                  |

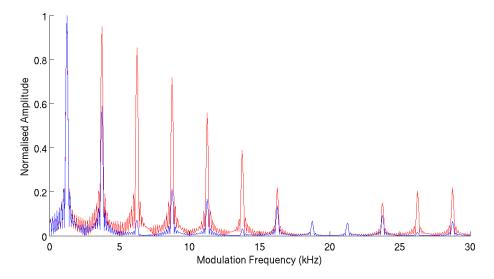

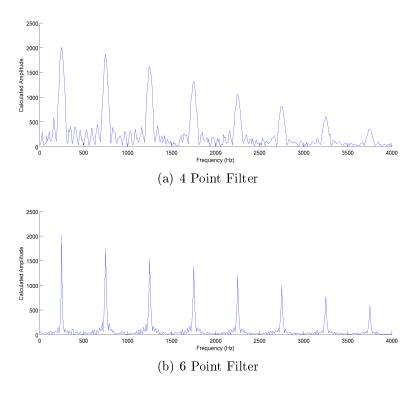

| 6.15 | Four Phase Pixel Frequency Response                                              |

| 6.16 | Four Phase Pixel Frequency Response (1.25 VR<br>eference) $$ 190                 |

| 6.17 | Imaging Optical Setup                                                            |

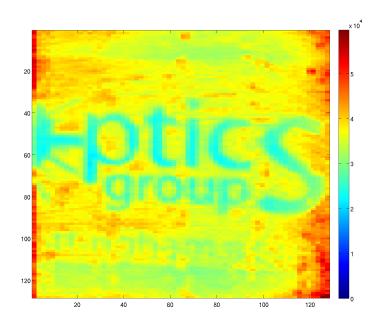

| 6.18 | Applied Optics Group Logo                                                        |

| 6.19 | DC Image (Time Pixel)                                                            |

| 6.20 | Two Phase Image (Time Pixel, No Modulation)                                      |

| 6.21 | Two Phase Image (Time Pixel)                                                     |

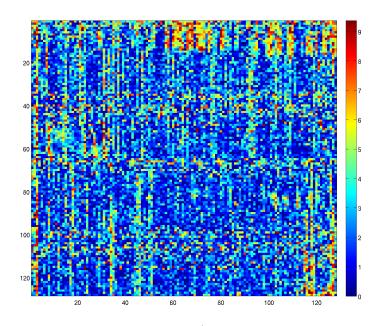

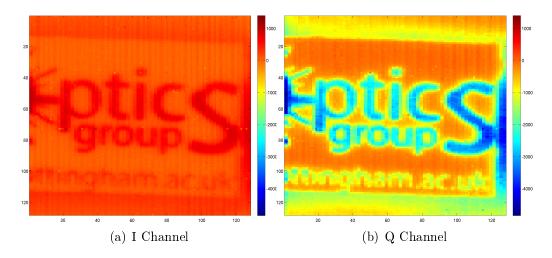

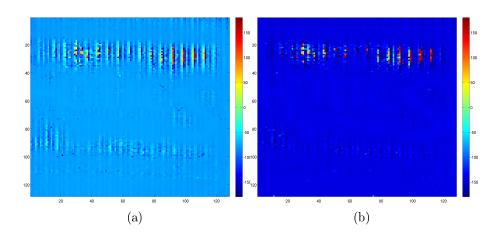

| 6.22 | Four Phase Raw Results                                                           |

| 6.23 | Four Phase Amplitude Image (Time Pixel)                                          |

| 6.24 | Four Phase Phase Image (Time Pixel)                                              |

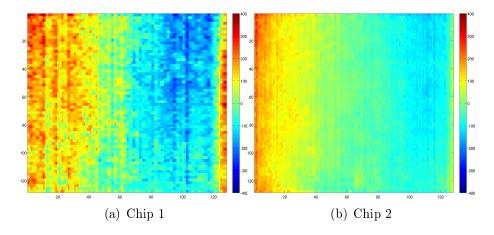

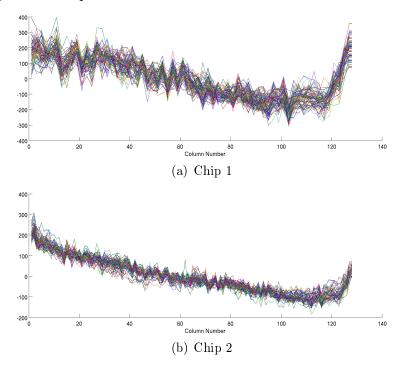

| 6.25 | Fixed Pattern Noise Image                                                        |

| 6.26 | Fixed Pattern Noise by Columns | • | • | • | • | • | <br>• | • | • | • | • |       | • | • | • | • | • | 198 |

|------|--------------------------------|---|---|---|---|---|-------|---|---|---|---|-------|---|---|---|---|---|-----|

| 6.27 | Fixed Pattern Noise by Rows    |   |   |   |   |   | <br>• |   |   |   | • | <br>• |   |   |   | • |   | 199 |

| 7.1  | Modulated Light Image          |   |   |   |   |   |       |   |   |   |   |       |   |   |   |   |   | 202 |

# List of Tables

| 2.1 | Modulated Camera Comparison               |

|-----|-------------------------------------------|

| 4.1 | Polysilicon Resistor Spacings             |

| 5.1 | Comparator Output Multiplexer Truth Table |

| 5.3 | Camera Chip Pinout                        |

| 5.4 | Pixel USB Block                           |

| 5.5 | 62 Bit Three Data Point Pixel USB Block   |

| 5.6 | 128 Bit Three Data Point Pixel USB Block  |

| 5.7 | Reduced Lookup Table Code Size            |

# Chapter 1

## Introduction

### 1.1 Introduction

This chapter describes the beginnings of photography and how it has developed to the present day whilst also introducing the idea of a camera that can measure modulated light. It also discusses the way in which optical detection is achieved on electronic chips with the advantages and disadvantages of each method. Lastly, the different noise sources that affect cameras are considered.

## 1.2 Project Aims

The motivation behind this work was to create a new type of modulated light camera using digital processing, capable of distinguishing both the amplitude and phase of an input light signal independently of any other light present. The focus was on having a fairly simple pixel which could be kept small so that the camera would have a high spatial resolution and a large array could be fabricated without requiring a large and expensive chip.

## 1.3 A Brief History of Photography

Since Louis Daguerre invented the first practical process for capturing an image in the late 1830s, the ability to record the visual world has had an enormous impact in every walk of life. Photography advanced quickly, with the wet plate process developed in 1850 by Frederick Scott Archer allowing exposure times to be reduced significantly, although with the disadvantage that the plates had to be created by the photographer. In 1855 the dry plate was invented, allowing plates to be commercially manufactured instead and then in 1884 the first film negatives were developed, simplifying the photographer's job even further.

The first colour photograph was made in 1861 by James Clerk Maxwell of a tartan ribbon, as can be seen in Figure 1.1, although it would not be until 1907 that colour plates would be commercially available.

Figure 1.1: First Colour Photo, by James Clerk Maxwell

In 1935, Kodak released its first colour film which used essentially the same technology in use in photographic films today. After these developments, cameras and film technology continued using the same ideas until 1981, when Sony developed a consumer camera using a charge coupled device (CCD) instead of film. This heralded the age of the digital camera.

Digital cameras use a CCD or photodiode array to detect light, whereas black and white film photography uses silver-halide crystals and colour film photography relies on coloured emulsions. Digital cameras offer the advantage over film cameras

that the image is immediately available, can be easily transmitted and can be post processed with ease. As they do not require film, digital cameras can be made to be very compact if required and are now largely ubiquitous, with most mobile phones including a camera of some description and dedicated digital cameras taking over from film cameras in most applications.

Cameras are not limited to taking single still images - films have been made since celluloid replaced the photographic plate. As well as capturing everyday life, films allow the world to be viewed differently through the use of high speed photography and time lapse photography. In the former, film is shot at a high rate and then played back at a much lower rate which allows details to be seen that would otherwise not be possible. One simple application of this was first used in 1878 to determine whether a horse had all of its feet off the ground during a gallop. Time lapse photography on the other hand takes pictures at a very slow rate and then plays them back at a normal rate to show the passage of time as a plant grows for instance.

In all of these cases, the camera is recording the instantaneous intensity of the light of a scene as we see it with our own eyes, even if it does give us more information than we would otherwise see. Making cameras with integrated circuits allows processing to happen at or very close to where the light is detected and so measure effects that would not be able to be seen in any other way. For example, in a typical experiment, light will be shone onto a sample which affects the light in some way and it is this change in the light that should be measured. Unfortunately, the signal is often so small that it is swamped by background light. In some cases the experiment could be carried out in the dark, but for the most part this is undesirable, and in many cases it is not possible to remove the background light as it is inherent to the experiment. However, if the light that is input to the experiment is modulated then it is possible to extract the signal by locking in to the frequency of the input and only considering frequencies that are near by. An image taken by a normal camera has only one parameter which is intensity. A modulated light signal at particular frequency has three quantities that can be measured, the offset (which equates to

the light intensity as measured by a normal camera), and the amplitude and the phase of the modulated light component. These are illustrated in Figure 1.2.

Figure 1.2: Modulated Light Parameters

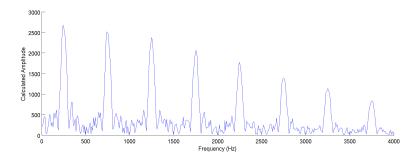

How this signal is recovered is considered in Chapter 3. Other types of modulated signal exist, namely those where a range of modulation frequencies may be present and the intent is to measure the intensity of all of those frequencies, in other words a basic Fourier transform is performed on the detected light signal [Kongsavatsak, 2005].

A camera that can measure the modulation amplitude or phase is known as a modulated light camera, or MLC. Where the camera is designed to measure the amplitude and/or phase of a known fixed frequency, the camera may also be referred to as a lock-in camera.

There are many situations where using modulated light is useful. In the simplest case, detecting the presence of modulation without needing to know the modulation amplitude or phase is sufficient. One such example is the measurement of sperm motility. Viable sperm produce a range of modulation frequencies up to around 1 kHz [Woolhouse, 1986]. By measuring the presence of modulated signals in this range, the number of potentially viable sperm can be counted and the paths which they take recorded, which is also a way of assessing viability [Comhaire et al., 1992]. It is also possible to envisage modulated light being used to help measure athlete

movements by placing small modulated light sources at positions on their bodies and recording both a standard image and a modulated light image. Doing so allows the movement to be isolated even in ordinary lighting. This is a very straightforward application because there are no real limitations on the frequency of the modulation and again, all that is being measured is the presence (and position) of the modulated sources.

Modulated light is often used in experiments to isolate the signal of interest from any background light. An example of an application where this is the case is in imaging the retina. The lens of the eye is imperfect and there are other factors which contribute to aberrations and mean that any potential image is of much lower quality than desired. Using a modulated light input the signal can be isolated from the background light and part of it then measured with a wavefront sensor to calculate the aberrations and correct for them using a deformable mirror [Stockford et al., 2007]. This application does not require high frequency modulation and indeed benefits from a lower frequency because the light levels are low and the deformable mirrors require a certain amount of time to move and produce the corrections. A modulation frequency of a few hundred Hz should therefore be sufficient.

It is possible to use modulated light detectors to measure range by calculating the phase between the modulation and the local oscillator, as described by many authors [Gruss et al., 1991, Gulden et al., 2001, Lange and Seitz, 2001] and as will be discussed in Chapter 2. This application requires high frequency modulation to obtain good range resolution. With a 100 MHz modulation frequency and a system capable of resolving phase within 1°, it would be possible to measure range with an accuracy of approximately 4 mm.

A final type of modulated detection is in measuring the frequency content of a signal. An example of this is described by Kongsavatsak [Kongsavatsak, 2005] for measuring the blood flow and concentration in skin. This type of camera is quite different to that proposed in this work because it does not work on lock-in techniques.

## 1.4 Electronic Photodetection

The photodetector in a camera takes photons and converts them into something else that is more permanent. In a traditional black and white camera film, the light sensitive silver halide grains are the photodetectors. If sufficient light is absorbed by a grain, it is converted to metallic silver and can be fixed in that state when developed, thus forming an image. In digital cameras, the photodetectors are a uniform array of pixels which are typically made up of charge coupled devices (CCDs) or photodiodes.

The design choices made for the photodetector are potentially the most important of the entire design; as they are the first stage of the device, any decisions here will impact on the whole of the design. The application that the camera will be used in is also important, for example if we want to create a device capable of the same resolution as a film camera then a small pixel size is needed, otherwise the device will become undesirably large. The equivalent pixel resolution of film is a hotly debated topic. Kodak use  $6.8\,\mu\mathrm{m}$  pixels in many of their CCD sensors. Professional quality film cameras can resolve at least 100 lines per mm, which equates to 200 pixels per mm or  $5\,\mu\mathrm{m}$ , so it appears as though CCD cameras are not that far behind film cameras in terms of feature size, but with 35 mm film having an image size of  $35\,\mathrm{x}\,24\,\mathrm{mm}$ ,  $5\,\mu\mathrm{m}$  pixels equate to a camera with 34.6 million pixels which is a long way beyond current consumer equipment.

Small pixels tend to suffer from worse noise performance (see Sections 1.6.2 and 1.6.6), and they leave little space for ancillary circuits alongside each pixel. Such ancillary circuits are desirable since including more circuitry in the pixel allows for more complex operations but of course reduces the area of the pixel that is light sensitive, also known as the fill factor. The fill factor is calculated as shown in Equation 1.1.

$$Fill factor = \frac{Light sensitive area of pixel}{Total area of pixel}$$

(1.1)

A high fill factor is desirable, because any light falling onto an area of the pixel that is not sensitive to light is wasted. It is possible to improve the effective fill factor significantly with the use of a micro lens array. The micro lenses are created with the same pitch as the pixels and focus the incoming light onto the photosensitive area of the pixel.

This section considers the different photodetectors available in standard CMOS processes and compares them to the charge coupled device (CCD). There are three types of photodetectors available in CMOS; the photodiode, the photogate and the phototransistor. First the process by which optical absorption occurs in semiconductors will be considered.

### 1.4.1 Optical Absorption in Semiconductors

In order to be able to measure light in an electronic device, it must be converted into electrons. Semiconductors can absorb photons and convert them into electron-hole pairs as follows.

In a semiconductor, the carriers that contribute to current flow exist in the conduction and valence bands. The conduction occurs in the conduction band as electron flow and also occurs in the valence band in the form of so called "hole" flow, where electrons moving within the valence band make it appear as though the hole, or lack of an electron, is moving in the opposite direction. To make an electron move from the valence band to the conduction band, it must be supplied with energy. For an optical detector, this comes in the form of light, or photons. A single photon has energy E = hv in electron volts (eV), where h is Planck's constant and v is the frequency of the light. For a photon to move an electron to the conduction band, it must have an energy of at least the bandgap (that is, the energy gap between the

conduction and valence bands) of the semiconductor,  $E_g$ . Assuming that this is the case, an electron-hole pair will be generated.

Semiconductors are split into two groups - those that have a direct bandgap and those that have an indirect bandgap. Direct bandgap semiconductors need only rely on a photon being absorbed to generate an electron-hole pair, whereas indirect bandgap semiconductors require extra help in the form of a phonon, or lattice vibration. This means that optical absorption in indirect bandgap semiconductors is much less effective than in direct bandgap semiconductors.

Knowing the bandgap of a semiconductor means it is possible to calculate what wavelengths of light it is sensitive to. For example, gallium arsenide (GaAs), a semiconductor often used in low noise, high speed applications has a (direct) bandgap of 1.43 eV. The energy of a photon has already been mentioned and can be rearranged to calculate the wavelength of light that can be detected by a given semiconductor:

$$E = hv$$

$$= \frac{hc}{\lambda}$$

$$\therefore \lambda = \frac{hc}{E_q}$$

(1.2)

Where c is the speed of light. With  $E_g = 1.43 \,\text{eV}$ , this gives  $\lambda = 868 \,\text{nm}$  as the longest wavelength of light that can be detected using GaAs.

Silicon has a bandgap energy of  $E_g = 1.11 \, \mathrm{eV}$ , so it can detect light of  $\lambda = 1.12 \, \mu\mathrm{m}$  and below, meaning both it and GaAs can detect visible light. Silicon is an indirect bandgap semiconductor however, so GaAs is a better optical detector in that a higher proportion of photons are converted into electron-hole pairs. A final example is gallium phosphide (GaP), that has a bandgap of  $E_g = 2.26 \, \mathrm{eV}$ , meaning it can detect light of  $\lambda = 550 \, \mathrm{nm}$  and below, so it is not sensitive to red or yellow light. GaP is used to make light emitting diodes, so not absorbing red or yellow photons is a useful feature.

The sensitivity of the semiconductor to light has a strong wavelength dependence. The material properties play a large role in how deep the light can penetrate and this directly affects how well the light can be absorbed. Figure 1.3 shows the depths to which light can penetrate in different semiconductors.

Figure 1.3: Semiconductor Absorption Coefficients [Sze and Ng, 2007]

Even when a photon of the correct energy strikes the detector, it may not cause an electron-hole pair to be generated. The ratio of the electron-hole pairs generated to the number of incident photons is known as the quantum efficiency and is wavelength dependent. Factors other than the material itself affect the number of photons converted into electron-hole pairs. For example, when a detector is fabricated on a chip, it will be covered by a number of transparent layers including the passivation layers that are placed over the entire chip for protection. These layers can absorb light and cause it to be reflected away due to the boundaries between the different layers, which means that the light reaching the detector is of a lower intensity than that which is incident upon the chip. The AMS C35 process has a manufacturing option to place a final layer on the chip that acts as an anti-reflection coating to increase the amount of light reaching the detectors and hence increase the responsivity.

In all cases, the photon being absorbed and an electron-hole pair being generated is not enough. Left to their own devices, the electron and hole will recombine in a short amount of time and there will be no useful effect. To generate a current flow, the electron and hole must be kept separated. This can be achieved by using a pn junction as the detector rather than just an intrinsic semiconductor. When the pn junction is reverse biased, the electric field across the junction will sweep any electrons generated near the junction into the n side and any holes generated into the p side, thus contributing to current flow.

The I-V characteristics of an illuminated pn junction are shown in Figure 1.4.

Figure 1.4: Illuminated pn Junction I-V Characteristics

When the junction is operating in the third quadrant it is reverse biased and a reverse current flows that consists of the dark leakage current and the photon generated current, also known as the photocurrent. This is the mode of operation when using the junction as a photo detector and the current flow is independent of voltage as long as the diode remains reverse biased. As the intensity of illumination changes, the curve moves up and down the y axis. This photodetector mode is also known as the photoconductive mode.

The pn junction can also operate as a photo cell. In the third quadrant, the junction is provided power by the external circuit whereas in the fourth quadrant, the junction provides power to the external circuit. This is also known as the photovoltaic mode and is the region used for solar panels.

The final quadrant of operation for a diode, the first quadrant, has the junction forward biased. This quadrant is used in rectifying circuits but is of no real interest in optical detection.

The following sections (1.4.2 to 1.4.5) describe the different ways in which the pn junction is utilised in devices for photo detection.

### 1.4.2 CMOS Photodiode

The photodiode is probably the most commonly used CMOS detector, being made of the simple pn junction. Every silicon process has a number of different silicon layers (as well as the metal and poly-silicon layers) that can be different thicknesses and different doping levels and types. This means that there are lots of possibilities for forming pn junctions that can then be used as a photodiode - in essence the only difference between a diode and a photodiode is that the photodiode is exposed to light. This further means that any pn junctions that are not intended for light detection, such as those in the majority of the transistors in a design, must have a light shield. As an example, the AMS C35 process has a p type substrate and a lightly doped n-well, as well as both p+ and n+ diffusions, which is the typical configuration for a single well CMOS process. In this case, there are three different photodiodes available, created through the combination of the different p and p layers. More complicated processes have extra layers for the creation of double or triple well structures and so allow for further pn diodes and the possibility of making more complicated diodes by using structures similar to p-p-p diodes.

The three diodes available in a single well process are all slightly different and offer individual advantages and disadvantages. They are the n-diffusion to p-substrate diode, the n-well to p-substrate diode and the n-well to p-diffusion diode.

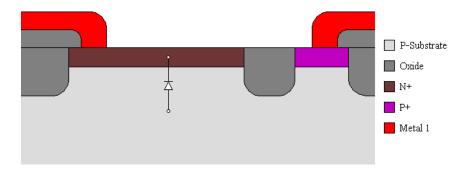

#### 1.4.2.1 N-Diffusion to P-Substrate

The n-diffusion to p-substrate diode, as shown in Figure 1.6, is sometimes referred to as a shallow diode due to its junction depth, which is  $0.2 \,\mu\mathrm{m}$  in the AMS C35 process. The shallow junction depth means that its sensitivity tends toward light with shorter wavelengths which is caused by photons penetrating further into silicon at higher wavelengths and so not being captured by the junction. Because the n-diffusion has high doping concentration the doping profile is relatively steep and so the depletion region at the junction is narrow, meaning that the diode has a high capacitance.

Figure 1.5: N-Diffusion to P-Substrate Diode

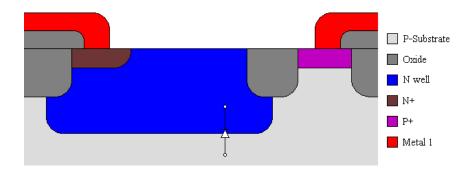

#### 1.4.2.2 N-Well to P-Substrate

The *n*-well to *p*-substrate diode, also known as the deep diode, has almost exactly the opposite characteristics of the shallow diode, with relatively low capacitance and better responsivity at higher wavelengths, as well as having a higher leakage current in reverse bias than the shallow diode. In the AMS C35 process the junction is  $3.5 \,\mu\text{m}$  deep. The cross section of the diode is shown in Figure 1.6.

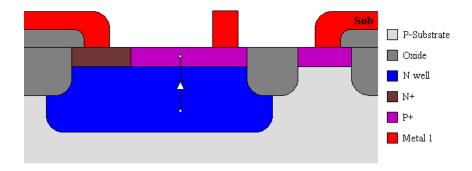

### 1.4.2.3 N-Well to P-Diffusion / Buried Double Junction

The n-well to p-diffusion diode, as shown in Figure 1.7, offers an attractive alternative to the previous two diodes as both the anode (A) and cathode (C) are able

Figure 1.6: N-Well to P-Substrate Diode

to be set at any voltage whereas one of the terminals in each of the previous two diodes was the substrate, which is connected to ground to ensure that the associated pn junctions remain reverse biased with no risk of latch-up occurring. Being able to connect each terminal to any point makes it possible to use the diode in less conventional setups (as both inputs to a differential mixer, or in the feedback path of an amplifier for example). In general this diode offers a similar performance to the n-diffusion to p-substrate diode however the additional deep junction formed by the n-well to p-substrate boundary means that it exhibits both long and short wavelength sensitivity [Pui, 2004], meaning an overall wider wavelength response and the possibility of colour detection [Lu et al., 1996].

As the primary junction is isolated from the substrate by the *n*-well, this device tends to have better immunity to cross talk from adjacent photodiodes or other devices nearby that are injecting charge into the substrate.

Figure 1.7: N-Well to P-Diffusion Diode

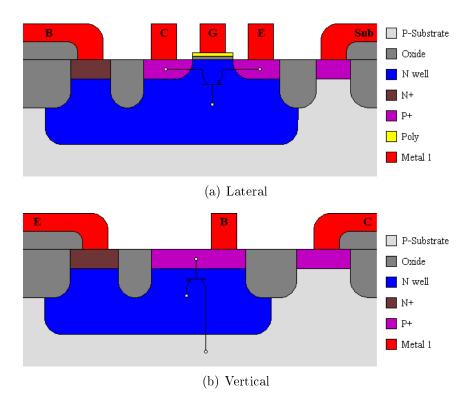

### 1.4.3 CMOS Phototransistor

An alternative to using a photodiode is to use a bipolar transistor as a photosensitive device. By arranging it so that the photons are absorbed near the base-collector junction, the device operates just as it would if a base current was applied directly. There are two types of bipolar transistors in a single well CMOS process; the lateral transistor, which is formed as a pnp device along the x-y plane of the chip and the vertical transistor which is formed as a pnp device with layers in the z plane of the chip. Both of these devices are typically treated as "parasitic", that is to say that they are not intentionally included but are only there because pnp structures occur anyway. They are modelled, but not as well as the FET devices and they tend to have relatively poor performance. The vertical transistor layout provided by AMS in the C35 process in particular has a very small current gain of around 6 at 100 nA compared to around 100 in a typical bipolar transistor and is also limited by having the collector tied to the substrate whereas the horizontal transistor can connect all terminals independently. As current gain is one of the primary reasons for using a phototransistor, the vertical device is of little interest in practical sensors. The horizontal transistor fares much better with a current gain of 76 at 100 nA whilst also occupying a smaller area.

The cross sections of the two configurations are shown in Figure 1.8. The lateral transistor has a fifth terminal which is very similar to the gate in a MOSFET. Its purpose is to separate the collector and the emitter diffusion during manufacturing by blocking the p+ implant which avoids having to resort to using field oxide. This keeps the effective base length as short as possible which helps increase its gain. When the device is being used, the gate is kept at  $0 \,\mathrm{V}$  so that it does not cause inadvertent conduction between the collector and emitter.

Figure 1.8: Bipolar Photo Transistor Cross Sections

## 1.4.4 CMOS Photogate

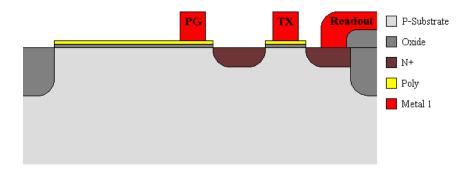

The photogate consists of an area of diffusion covered in a gate and a read out transistor, as shown in Figure 1.9. The operation of the photogate differs from the diodes and transistors already mentioned in that it is always used in a charge integration mode. The first stage of the measurement involves the n+ diffusion between the PG and TX terminals being emptied of charge, followed by a high voltage being applied to the diffusion gate, PG. The high voltage creates a strong field which collects any electrons generated by the illumination and accumulates them in the n+ diffusion. The photogate PG is held high for the integration period and then the charge is read out by activating the read out transistor to transfer the accumulated charge to a charge amplifier.

The photogate has the disadvantage that the light sensitive area is covered by the gate. Although this is transparent, it still reduces the amount of light reaching the well.

Figure 1.9: Photogate

## 1.4.5 Charge Coupled Device (CCD)

It is not possible to discuss photodetectors without mentioning the charge coupled device (CCD). First invented by George Smith and Willard Boyle in 1969 CCDs rapidly overtook NMOS sensors (and CMOS sensors when they became available) due to their better sensitivity. Since then CCDs have been further optimised and can achieve noise levels of just a few electrons over long integration times. CCDs operate in a similar way to the photogate in that electrons are collected in a well and then transferred out to be read. A CCD array will transfer the charge from a given pixel across the array from pixel to pixel until it reaches the output stage and so they are manufactured on specialised processes which is optimised for this charge transfer. The disadvantage of this type of process is that the MOS transistors perform poorly so cannot be used for constructing ordinary circuits and there is little scope for combining a photodetector and processing circuitry into each pixel.

### 1.5 CMOS Pixel Sensors

#### 1.5.1 Passive Pixel Sensor

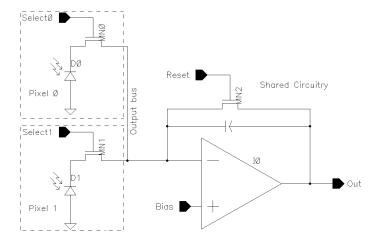

The passive pixel sensor (PPS) can be regarded as the first MOS pixel. Introduced in 1967 [Weckler, 1967] each pixel consists of a photodiode and a single transistor which is used as a switch to select the pixel. Figure 1.10 shows two pixels, which

consist of D0 and MN0, and D1 and MN1. In addition to the array circuitry, charge amplifiers are included at either the column or array level (shown here as I0).

Figure 1.10: PPS Schematic

The PPS operates by making use of the inherent capacitance of the photodiode as a storage element. The selected pixel is first primed by using MN2 to "reset" the selected photodiode and the charge amplifier capacitor. This is done by turning on MN2 when the output is connected to  $V_{DD}$ , whereby the voltage across the photodiode will be charged to  $V_{DD}$ . When MN2 is turned off, the capacitance will discharge due to the current caused by the incident illumination. Sampling the output a fixed duration after the reset allows the light intensity to be measured.

As the PPS only has a single transistor at the pixel it is very attractive for making cameras; even with small pixels the area of the pixel that is not light sensitive will be minimised and so lead to a more efficient use of the available light. However, it is not possible to access each pixel at once so an array using PPS pixels will suffer from a rolling shutter effect where there is a finite amount of time between each pixel being sampled and so anything in the scene that is moving quickly will be distorted. A more substantial problem with the PPS is that when a given pixel is selected, the photodiode is connected to the output bus directly and so it must drive the bus capacitance as well. This reduces the speed at which a PPS can operate. As already mentioned, the signal is caused by the photodiode capacitance discharging due to the photocurrent, but now the photodiode is connected to a large additional

capacitance and as a result the pixel will take more time to discharge to the same point than without the additional capacitance, given the same photocurrent.

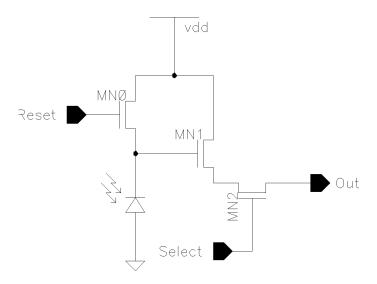

#### 1.5.2 Active Pixel Sensor

Strictly speaking any pixel that has a buffer, amplifier or other device intended to improve the pixel performance, where that device is integrated directly at the sensor is an active pixel sensor (APS), however the term is commonly used to describe an integrating pixel as described below. Adding a buffer means that the reset device must also be included at the pixel. This increases the in-pixel device count from a single transistor to three transistors, but removes the problem of the high column bus capacitance exhibited by the PPS. The APS was first proposed by Chamberlain in 1969 [Chamberlain, 1969].

Figure 1.11: Three Transistor APS Schematic

Figure 1.11 shows the in-pixel circuitry of the three transistor APS. MN0 is the reset transistor that is equivalent to transistor MN2 in the PPS. MN2 is the select transistor and MN1 is the top half of a source follower buffer, where the bottom transistor of the follower is common for the entire column and is not shown in this figure. Splitting the follower in this way has a number of advantages: it keeps the fill factor high by removing the need for an additional transistor and the associated

bias wire. A further advantage of having the bottom half of the follower shared per column is that by definition each pixel in the column must use that device. In the case where each pixel had a complete buffer, although the drawn size of the transistors would be identical there would still be mismatch. It also lessens matching problems as the bottom transistor is common to all pixels in a column. Using a shared transistor like this reduces mismatch between pixels; if each pixel contained a complete buffer then the slight mismatch between the size and other parameters of the buffer transistors from pixel to pixel would cause a different voltage offset at each pixel, manifesting itself as increased fixed pattern noise (see Section 1.6.5). With a shared transistor this mismatch is removed for a column, although the other buffer transistor in the pixel still has the same effect, and there is still column to column mismatch. Taking this technique to its extreme would result in a single transistor shared as the bottom half of the source follower for the entire array, which would result in a reduced fixed pattern noise at the expense of a greatly reduced frame rate caused by each pixel having to be integrated and sampled individually rather than a row at once.

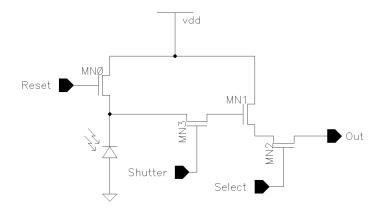

A camera using the three transistor APS suffers from the same problem as one using the PPS, namely that only a single pixel (or row of pixels) can be accessed at once and these is no storage at the pixel so it has a rolling shutter. Unlike the PPS, it is possible to circumvent this problem by adding a further transistor to the pixel, at the trade off of fill factor, as shown in Figure 1.12. The extra transistor is used as a shutter to sample the photodiode voltage onto the small gate capacitance of the output buffer. Applying the shutter to each pixel at the same time removes the rolling action whilst still allowing the results to be read serially.

#### 1.5.3 Linear Pixel

It is often desirable to be able to make continuous time measurements of light level, something not possible with the PPS or APS due to their integrating behaviour.

Figure 1.12: Four Transistor Shutter APS Schematic

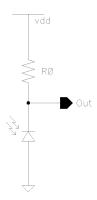

In fact, the very first solid-state image sensors developed in the 1960s produced continuous time measures of illuminance. For example, Schuster and Strull produced a  $50 \times 50$  array of phototransistors in 1966 [Schuster and Strull, 1966]. To amplify the signal to a useful level, a gain element must be included in non-integrating detectors. By placing a resistor in series with the photodiode, as shown in Figure 1.13, the photocurrent will be converted into a voltage at the Out terminal as per Ohm's law. This means that the gain, or transimpedance, of the pixel is determined by the value of the resistor. Assuming that the resistor is linear, the output voltage will also be linear with photocurrent.

Figure 1.13: Linear Pixel Schematic

The fact that the gain is determined by the resistor can also be a disadvantage; to convert typical photocurrents in the pA - nA range to useful voltages of at least mV means that the resistor must be of the order of  $1 \,\mathrm{G}\Omega - 1 \,\mathrm{M}\Omega$ . By examining minimum width resistors made of high-resistance polysilicon using the manufacturer provided design kit it was found that a  $1 \,\mathrm{M}\Omega$  resistor would consume a silicon square

$35 \,\mu\mathrm{m} \,\mathrm{x}\, 35 \,\mu\mathrm{m}$  and a  $200 \,\mathrm{M}\Omega$  resistor, would be  $565 \,\mu\mathrm{m} \,\mathrm{x}\, 565 \,\mu\mathrm{m}$ . Clearly fabricating a  $200 \,\mathrm{M}\Omega$  resistor in an array would be extremely impractical, but in some cases a  $35 \,\mu\mathrm{m}$  square might be feasible. Of course, this is using a minimum width device which means that the pixel to pixel variation in resistance could be quite significant, with a corresponding increase in fixed pattern noise. Using a wider resistor would reduce this variation at the expense of increasing the area required.

A further problem with using a device with such a large area is that in addition to the desired resistance there is also an undesired capacitance. As both parameters are increasing at the same time they have a negative effect on the cut off frequency of the pixel. For example, the  $1\,\mathrm{M}\Omega$  resistor already described has an associated parasitic capacitance of 93 fF, resulting in a cut off frequency of around 1.7 MHz. Simply changing the width of the resistor from  $0.8\,\mu\mathrm{m}$  to  $2\,\mu\mathrm{m}$  to reduce mismatch, whilst leaving the resistance the same gives a parasitic capacitance of 470 fF and a cut off frequency of around 340 kHz.

The linearity of the output is both an advantage and a disadvantage. On one hand, a linear response is almost always easier to work with, but on the other hand, the dynamic range is limited directly by the available voltage range.

Because of these reasons using linear resistors in a pixel using the typical fabrication processes available today is not particularly feasible.

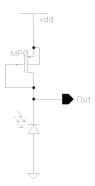

# 1.5.4 Logarithmic Pixel

An alternative to the integrating APS is to use a transistor in place of the resistor in the linear pixel and this means that a large transimpedance can be obtained in a relatively small area at the expense of sacrificing the linearity of the response to photocurrent. Because the transistor is operating in the sub-threshold region, the voltage output has a response proportional to the logarithm of the photocurrent [Chamberlain and Lee, 1984]. Although this is a disadvantage in many situations,

it can also be of benefit as well; a logarithmic response increases the dynamic range of the sensor and more closely matches the response of the human eye which are both useful features in real life scenarios. The logarithmic pixel is shown in Figure 1.14.

Figure 1.14: Logarithmic Pixel Schematic

#### 1.5.5 Feedback Pixel

The feedback pixel (shown in Figure 1.15) is an improvement on the logarithmic pixel presented by Perelman [Perelman and Ginosar, 2001]. As the name suggests, a feedback amplifier is added to the pixel. The feedback is used to drive the gate of the load transistor with the aim of improving the frequency response of the pixel. The load transistor still works in the sub-threshold region so the pixel is still a log pixel, but the feedback works to ensure that any voltage swing appears at the output of the feedback amplifier. This corresponds to an increase in the usable frequency of the pixel as the capacitance being driven by the feedback amplifier, namely the gate of the load transistor and the drain of the select transistor, is much smaller than the capacitance of the photodiode.

## 1.6 Noise

Noise in all its forms degrades the performance of a system and so it is important to know about its causes and what can be done to minimise it. Temporal noise

Figure 1.15: Feedback Pixel Schematic

components are thermal noise, shot noise and flicker noise. Fixed pattern noise is a spatial noise component. Each of these noise components will be discussed in more detail now.

#### 1.6.1 Thermal Noise

The random motion of electrons in resistive material causes small voltage fluctuations. As would be expected, higher temperature (causing more active motion) and higher resistance both result in higher thermal noise. A resistive material will experience thermal noise on the voltage at its terminals according to Equation 1.3.

$$V_{thermal(rms)} = \sqrt{4kT\Delta fR}$$

(1.3)

Where k is Boltzmann's constant,  $1.38 \times 10^{-23} \, \mathrm{J/K}$  , T is the temperature in Kelvins,

$\Delta f$  is the bandwidth (Hz) under consideration and R is the resistance of the material in Ohms. As there is no current term, it can be seen that thermal noise is present even if there is no current flowing through the conductor. As k and R are constant for a given piece of conductor, the important factors here are the temperature and the bandwidth of the system and by reducing them the thermal noise contribution can be reduced. It is important to note that it is the bandwidth of the system that is important, not the frequency of a signal that it is trying to measure. This is because thermal noise is white noise, that is to say that it has uniform power contribution at all frequencies (up to around 6000 GHz [Maas, 2005]).

A good example of an application where thermal noise reduction is essential is found in astronomical imaging, where the image sensor is typically cooled to cryogenic temperatures and the images are acquired over a long period to help reduce the contribution of thermal noise.

#### 1.6.2 Shot Noise

Shot noise occurs in both electronics and optics. In both cases it is caused by the fact that the energy is being carried by discrete packets (electrons and photons respectively) and that the arrival of these packets is random. In a pn junction, the DC current flow consists of the electrons and holes moving across the junction. As the holes and electrons move in a random direction, they will only cross over the junction if they have enough energy to do so for the direction that they are travelling, which is completely random. Equation 1.4 gives the shot noise magnitude for a DC current I and and bandwidth  $\Delta f$ , where q is the electron charge.

$$i_{rms} = \sqrt{2qI_{DC}\Delta f} \tag{1.4}$$

Shot noise is the often the greatest contributor to noise in a semiconductor device and as it is caused by the current flow rather than the device itself there is not much that can be done to reduce it apart from reducing  $I_{DC}$ .

The shot noise in an integrating detector such as the PPS or APS is proportional to  $\sqrt{N}$ , where N is the number of electrons captured (with a maximum determined by the well capacity of the detector) and is given in Equation 1.5, where C is the capacitance of the photodiode, V is the voltage across the device at full capacity and q is the electron charge.

$$N = \frac{CV}{q} \tag{1.5}$$

This allows the dynamic range of the pixel to be calculated:

Dynamic range =

$$N/\sqrt{N}$$

=  $\sqrt{N}$  (1.6)

So to increase the dynamic range of a detector, the well capacity must be increased. Although this can be done by increasing the maximum voltage used across the detector, this does complicate the design due to the need to cope with an extra supply voltage. Processes with the main supply voltage beneath 5 V often offer a "thick oxide" transistor that can be used at a higher voltage and are intended for interfacing with the outside world. For example, 3.3 V processes may offer a 5 V option and 1.8 V processes may offer 3.3 V. Both of these possibilities give the option of a reasonable increase in well capacity at the expense of fill factor (the thick oxide transistors occupy more space and require extra control lines) and complexity. Even higher voltages are possible using a dedicated high voltage process rated to 50 V for instance, but this is a move away from the common and inexpensive CMOS process and high voltages are more difficult to deal with.

The other way to increase the well capacity is of course to increase the capacitance of the detector which can be done by either using a device with a greater capacitance per unit area or else increasing the area of the device. Increasing the capacitance per unit area implies decreasing the junction depth (so changing from an *n*-well to *p*-substrate diode to a *n*-diff to *p*-substrate diode for example), but this has implications for the other characteristics of the device and so may not be an option. So the simple solution is to increase the area of the device. In fact there are no real disadvantages to this from a sensor point of view since both the dynamic range and the fill factor will increase. The disadvantages are cost, due to the increased area required, and a larger chip may not be compatible with existing optical systems.

With the desire for larger numbers of pixels per camera in a standard size device, the pixel size decreases and hence the well capacity decreases as well. Typical CCDs have a well capacity on the order of  $10^5 - 10^6$  electrons. The Kodak KAF-3200 sensor, for example, has a limit of 55 000 electrons, giving a shot noise limited dynamic range of 235, or 7-8 bits resolution [Kodak, 2007].

## 1.6.3 Flicker Noise (1/f)

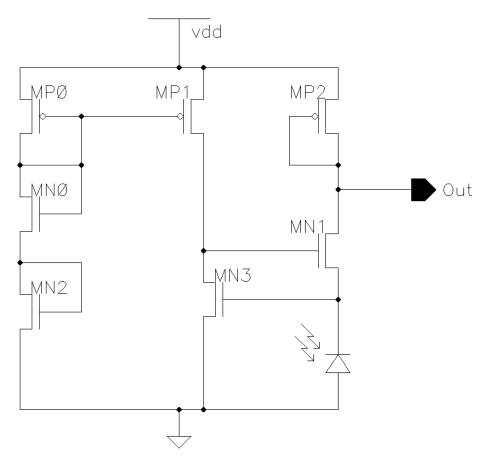

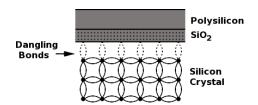

Flicker noise is present in all semiconductor devices. Although it is not fully understood it is related to carrier recombinations at the surface and the interface between the silicon and the oxide above it [Sze and Ng, 2007]. The atoms at the edge of the silicon do not have a full set of bonds by definition. The remaining bonds are left dangling (see Figure 1.16) and these bonds mean that electrons are more likely to be trapped randomly at the interface.

Figure 1.16: Oxide-Silicon Interface [Razavi, 2001]

The electrons being trapped and released manifest themselves as noise with an unusual spectral response in the form of  $1/f^{\alpha}$ , where  $\alpha \approx 1$ , in other words flicker noise

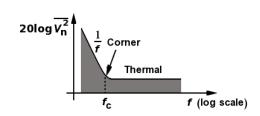

is dominant at low frequencies. The concept of the flicker noise corner becomes useful here. As the contribution to the overall noise content from flicker noise decreases with frequency, there will come a point at which it is no longer a significant factor. This is illustrated in Figure 1.17, where  $f_C$  is the corner frequency.

Figure 1.17: Flicker Noise Corner Frequency [Razavi, 2001]

The corner frequency can be calculated with Equation 1.7 [Razavi, 2001], where K is a process parameter close to  $10^{-25} \,\mathrm{V^2F}$ , k is Boltzmann's constant and T is the temperature in Kelvins.

$$f_C = \frac{K}{C_{cr}WL} \cdot g_m \cdot \frac{3}{8kT} \tag{1.7}$$

Taking  $C_{ox}=4.54\,\mathrm{fF}/\mu\mathrm{m}^2$  [AMS, 2004] with a NMOS transistor  $1/1\,\mu\mathrm{m}$ ,  $f_C$  can be as high as 158 kHz.

This is particularly important when taking many types of measurement since the rate of change of the parameter being measured can be very low. By using a modulated light input as a carrier to shift the signal away from the flicker noise, the noise performance of the system can be greatly improved. To reduce the effect of flicker noise, the simple solution is to use as large a device as possible within the parameters of how the circuit should work.

#### 1.6.4 Dark Current

Although diodes are often treated as having no current flow when in reverse bias, they do actually suffer from a small leakage current that depends on the type of the diode, its area, the length of its periphery and its reverse bias voltage. This means that a photodiode will still have a small current flow, even when not illuminated at all (hence "dark current"). When there is photo current flowing in the device the dark current manifests itself as an additional current component. The values of current involved are very small, for example a  $50 \times 50 \,\mu\text{m}$  n-well to p-substrate diode in the AMS C35 process reverse biased at 3.3 V has a leakage current of 8.5 fA and an identically sized n-diffusion to p-substrate diode has a leakage current of 1.4 fA. The dark current itself is constant and so will be removed by the demodulation process, but it will provide an additional contribution to the shot noise of the diode. The dark current is also dependent on temperature and an increase can have very noticeable effects. Schanz et al. reported a decrease in dynamic range of 10 dB at 85°C caused by the increase in leakage currents [Schanz et al., 2000].

## 1.6.5 Fixed Pattern Noise

Fixed pattern noise (FPN) differs from the noise sources described so far in that it is a spatial variation on a chip. Fixed pattern noise occurs because not all devices are identical, even when they are designed to be so. CMOS in particular has problems with supposedly identical transistors having voltage offsets of the order of tens of millivolts when under the same stimulus. These offsets are a particularly significant problem in symmetrical circuits such as differential pair amplifiers or Gilbert cell mixers but are a problem wherever two or more devices should be identical, such as the transistors in a camera array. The offsets can be reduced with careful layout techniques, with moderate matching producing offset voltages of around  $\pm 5\,\mathrm{mV}$  [Hastings, 2001], but it is not possible to remove them completely. The use of laser trimming of the device after manufacture allows much better matching to be achieved, on the order of  $\pm 1\,\mathrm{mV}$ , but this is only really suitable where a small number of devices need correcting. All types of devices have similar problems, not just transistors. Essentially, it is not possible to ensure that any two devices are exactly identical and so each stage of circuitry adds a further contribution to FPN

simply by adding a greater number of devices.

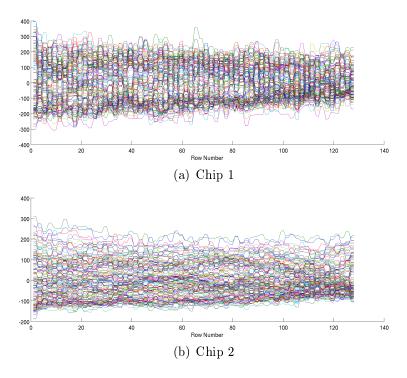

A example of how FPN can appear in a camera is shown in Figure 1.18. The figure shows a part of a uniformly illuminated camera (the design from Chapter 5) that has a so-called column based design, where the readout and amplification circuitry for a particular column is shared for all of the pixels in that column. This means that any variations in the readout circuitry manifests itself as vertical stripes in the image. The variation of the circuitry within the pixel itself is also shown as the difference in intensity moving up a column.

Figure 1.18: Example of FPN

Process variations are typically considered in two different scenarios, the variation across a chip and the chip to chip variation, also known as mismatch and process variations respectively. The process variation is caused by the relatively large difference in the environment for chips in different positions on a wafer whereas the mismatch is the random changes that lie around the process variation. A simple way to view this is as though the process variation is the mean of the mismatch variation, where the mean changes from chip to chip. The process variation has a much greater effect than the mismatch variation.

Because FPN produces a static variation in time, it is often possible to calibrate the camera by illuminating it with uniform intensity and subtracting the mismatched values from any subsequent images. This also means that the effects of FPN will be

usually reduced when measuring the amplitude or phase of a modulated signal with a modulated light camera. Since modulated light cameras are essentially looking at the variation between subsequent signals, a constant offset should have little effect on their results. A case where fixed pattern noise could be a problem with modulated light cameras is with the logarithmic pixel design. If the FPN manifests itself as a change in the amount of DC current flowing through the pixel then the AC gain of the device would also be changed.

#### 1.6.6 Reset Noise

Reset noise affects the integrating type of pixel sensors, where the photodiode capacitance is charged up through a switch. As the switch is resistive, thermal noise will be introduced on to the capacitance and when the switch is opened this noise will remain present along with the desired voltage. The level of the noise is independent of the value of the switch resistance and is actually mainly determined by the value of the photodiode capacitance, C, as shown in Equation 1.8, where k is Boltzmann's constant and T is the temperature in Kelvin [Razavi, 2001].

$$v_{rms} = \sqrt{kT/C} \tag{1.8}$$

Reset noise is often the limiting noise for integrating sensors, especially when the photodiode is small.

## 1.6.7 Noise Reduction

In addition to the general ways of reducing noise described, there are other techniques more specific to sensor design. Integrating pixels can utilise a number of techniques which can help to reduce the noise contributed from different sources. A technique called data double sampling (DDS) simply takes the results of two consecutive results and averages them which helps reduce the effect of any random noise,

but does assume that the illumination on the detector has not changed between the two samples and does not remove the effect of reset noise. A more complicated technique is correlated double sampling (CDS). This involves taking two samples per integration, where the additional sample is taken just after the reset period. The values are then subtracted from each other to remove the unknown reset noise. CDS can also help reduce FPN and is a more desirable solution than calibration because it does not require any additional storage or post-processing. Some techniques for reducing reset noise are available [Fowler et al., 2006], whereby a greater degree of control is used for the reset to control either the capacitance, bandwidth or the charge on the sensor capacitance, but all of the methods require more circuitry in the pixel and more complicated control which both contribute to reducing the fill factor.

# 1.7 Summary and Thesis Layout

This chapter has introduced the background to the project and provided a grounding in the basics of electronic photodetection by describing how semiconductors can be used as light sensors by absorbing light as photons and converting the photons into electron-hole pairs. These electron-hole pairs are the photocurrent which can be converted into a voltage using one of the pixel designs described in Section 1.5. Sources of noise which affect electronic circuits have been introduced, along with some ways in which they can be reduced. The idea that modulating the amplitude of a light signal is beneficial for being able to detect small signals, particularly in the presence of high background light has also been introduced.

Chapter 2 provides an overview of previous work carried out in the area of modulated light cameras. The different implementations of modulated light cameras are discussed as are their applications. Some cameras not originally designed for use as a modulated camera are also presented as being suitable for that purpose. Chapter

3 describes the theory and operation of lock-ins and modulation in general terms and more specifically when used in optical systems. It considers the different ways that it is possible to implement a lock-in and what the important characteristics to take into account when designing a lock-in are. It also applies this theory to the designs already mentioned in Chapter 2. Chapter 4 introduces the new lock-in pixel design and shows the designs fabricated on three prototype chips. Results are presented which demonstrate the pixel designs successfully operating as a lock-in. Chapter 5 discusses the final design fabricated, a 128x 128 pixel camera and the specific issues with scaling up to a large array. Chapter 6 contains the experimental results obtained from the camera chip and Chapter 7 provides the conclusion to the thesis.

# Chapter 2

# Modulated Light Camera Review

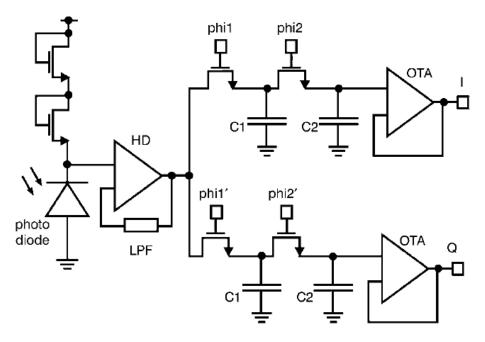

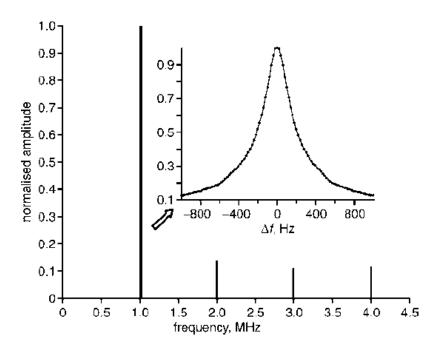

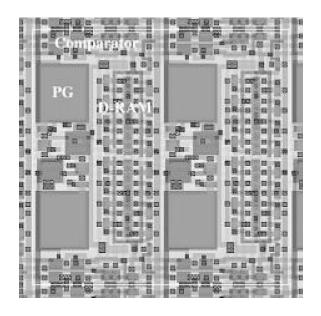

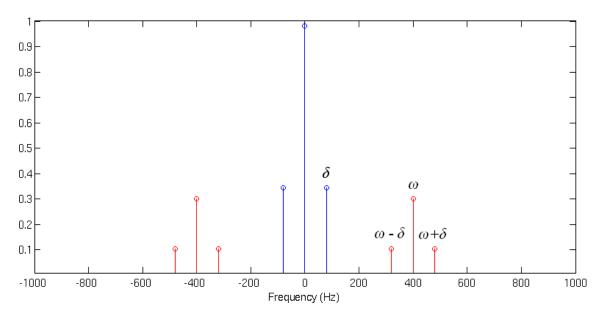

## 2.1 Introduction