Difference between revisions of "Vlsi:Cadence Tips"

(Added a summary of Voltage Storm analysis procedure.) |

(RC Extraction for C35/S35/H35 in IC 6.1) |

||

| Line 29: | Line 29: | ||

* It may be necessary to load a resource file in your LSW to get the layers to display in a nice format. From the LSW, choose '''Edit >> Resource Editor''', and from that window choose '''File >> Load''' | * It may be necessary to load a resource file in your LSW to get the layers to display in a nice format. From the LSW, choose '''Edit >> Resource Editor''', and from that window choose '''File >> Load''' | ||

* The voltage variation is shown in the form of a colour map on the extracted layout window. | * The voltage variation is shown in the form of a colour map on the extracted layout window. | ||

| + | |||

| + | == RC Extraction for C35/S35/H35 in IC 6.1 == | ||

| + | |||

| + | To run RCX successfully, you must first pass LVS correctly as normal. Do this by running LVS without any switches. If you run RCX now, it will fail. Now carry out LVS with the switch "resimulate_extracted" to guarantee that also substrate shorts are found correctly. RCX will run without any problems (note that you must not use the "resimulate_extracted" switch for normal LVS runs as it may give false results. | ||

Revision as of 11:10, 4 February 2009

Contents

Virtual Connections in Assura LVS

If you have two wires on a layout that are unconnected but will be connected together in a higher level then place a pin on both wires. When running Assura LVS you need to set some further options. Enable "View avParameters" and then click "Modify avParameters...". Find the "joinPins" option, enable it ("Use in run") and set it to "Top". Click OK to close the avParameters window. Now enable "View Additional Functions" followed by "Use joinableNet Function". Now click "Modify joinableNet Function...". In the new window enable "root cell?" then add your net to the "Net Names to Join" box and click "Add to Command List (below)" to add it. Click OK to close the joinableNet window and then run LVS as normal.

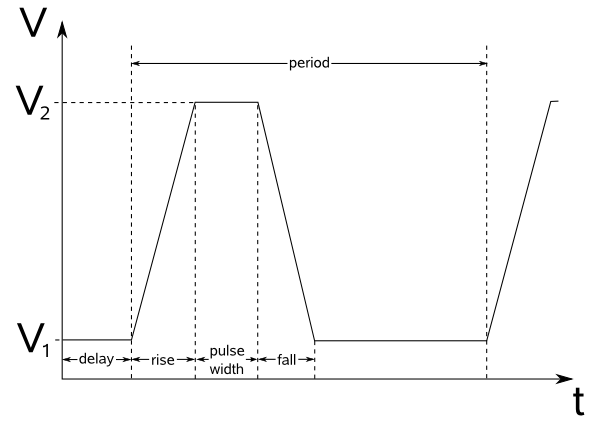

Voltage / Current Pulse Sources

I can never remember which voltage/current is which, so I've created an image to remind me:

Voltage Storm Analysis

Voltage Storm is a tool that allows the analysis of IR drops. For example, it can be used to monitor the distribution of VDD across an array of pixels. Follow this procedure for the analysis:

- Create your schematic and layout.

- Make sure your labels are in the center of any path or metal or poly they are on.

- From the Create menu, choose Pins from labels... and click OK to create pins on the layout.

- Run LVS from Assura, and then run RCX to generate the extracted view. You may need to use the JoinableNet function if you haven't joined some nets together.

- In the RCX window, choose to extract RC and use infinite Max Fracture Lengths squares in the Extraction tab, and enable extract parasitic resistor width (Netlisting Tab).

- Set up a test bench configuration, containing the extracted view. Use the hierarchy editor.

- Run a simulation that uses the extracted view. A short transient, AC or DC simulation is fine.

- From your Spectre ADE window, choose Session >> Schematic Window to open the test cell, and descend into the extracted view. This makes sure that you are in context.

- From the extracted view menu, choose Tools >> Voltage Storm from the menu.

- Select from the EM and IR menu, IR Drop Analysis

- Accept the use of the presistor (default)

- If all was correctly set up, your pins and available signals will be listed. Select the pins or signals of interest, using the CTRL key for multiple selections.

- Enter or browse to your simulation directory.

- Highlight one of the simulations in the list box.

- Press OK. The tool will perform some operations (can be seen in the CIW), and an IR Voltage Drop Results window will pop up.

- This allows you to choose on of those pins/signals chosen earlier, and study the drop.

- To display the voltage distribution, click one of the buttons near the bottom of the form. Hide layers, Display highlights is particularly useful.

- It may be necessary to load a resource file in your LSW to get the layers to display in a nice format. From the LSW, choose Edit >> Resource Editor, and from that window choose File >> Load

- The voltage variation is shown in the form of a colour map on the extracted layout window.

RC Extraction for C35/S35/H35 in IC 6.1

To run RCX successfully, you must first pass LVS correctly as normal. Do this by running LVS without any switches. If you run RCX now, it will fail. Now carry out LVS with the switch "resimulate_extracted" to guarantee that also substrate shorts are found correctly. RCX will run without any problems (note that you must not use the "resimulate_extracted" switch for normal LVS runs as it may give false results.